# Bit-Sice Design: Controlers and ALUs

Copyright © 1981 by Garland Publishing, Inc.

All rights reserved. No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means—graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems—without permission of the publisher.

Figures reproduced with the permission of Advanced Micro Devices.

15 14 13 12 11 10 9 8 7 6

#### Library of Congress Cataloging in Publication Data

White, Donnamaie E.

1942-

Bit-slice design.

Includes index.

1. Bit slice microprocessors—Design and construction. I. Title.

TK7895.M5W49 621.3819'58'2 79-7465

ISBN 0-8240-7103-4

Published by Garland STPM Press 136 Madison Avenue, New York, New York 10016

Printed in the United States of America

# Contents\_

| Pr | Preface                                                                                                                                               |  |                                              |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------|--|--|

| 1  | Introduction Selection of the Implementation Microprogramming Advantages of LSI                                                                       |  | 1<br>1<br>5<br>6                             |  |  |

|    | The 2900 Family Language Interrelationships Controller Design                                                                                         |  | 6<br>7<br>12                                 |  |  |

| 2  | Simple Controllers Sequential Execution Multiple Sequences Start Addresses Mapping PROM Unconditional Branch Conditional Branch Timing Considerations |  | 19<br>21<br>23<br>24<br>24<br>26<br>28<br>30 |  |  |

# vi Bit-Slice Design

| 3 | Adding Programming Support to the Controller | 43       |

|---|----------------------------------------------|----------|

|   | Expanded Testing                             | 43       |

|   | Subroutines                                  | 43       |

|   | Nested Subroutines                           | 47       |

|   | Stack Size                                   | 49       |

|   | Loops                                        | 49       |

|   | Am2909/11                                    | 52       |

|   | CASE Statement (Am29803A)                    | 53       |

|   | Microprogram Memory                          | 55       |

| 4 | Refining the CCU                             | 61       |

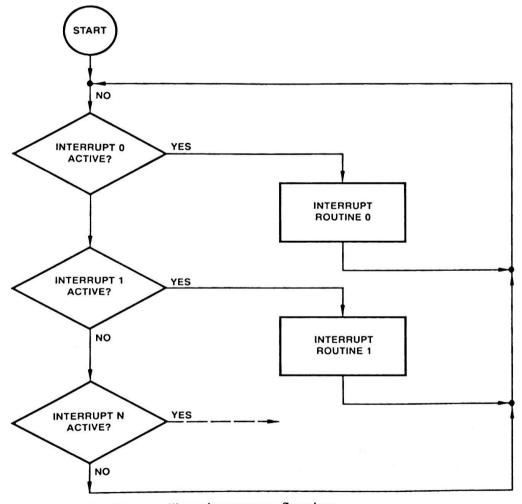

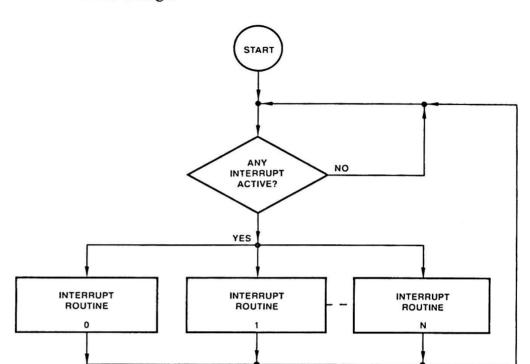

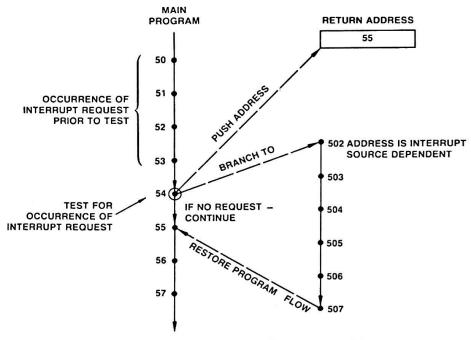

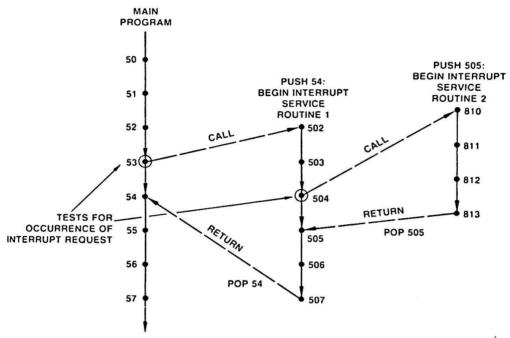

|   | Status Polling                               | 61       |

|   | Interrupt Servicing                          | 63       |

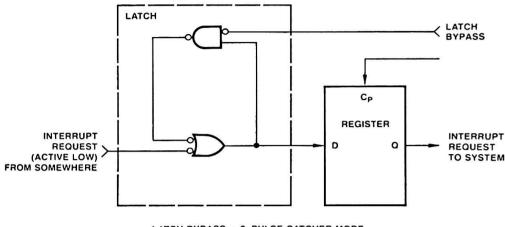

|   | Implementation                               | 63       |

|   | Am2910<br>Am2910 Instructions                | 70<br>71 |

|   | Control Lines                                | 81       |

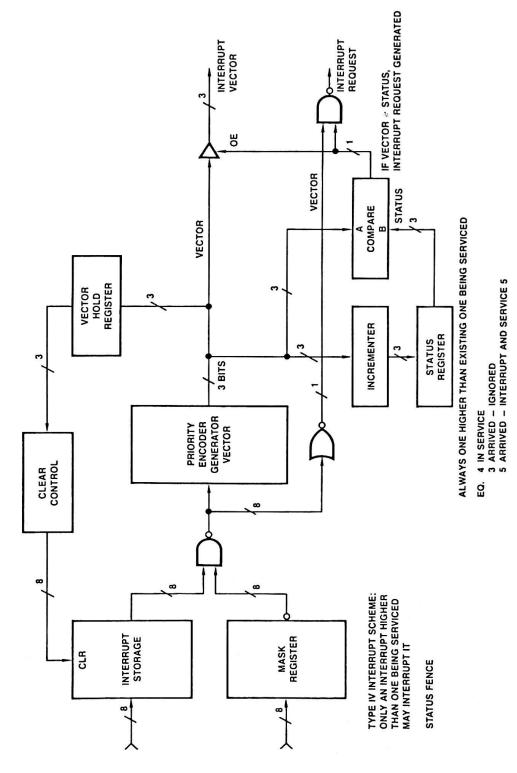

|   | Interrupt Handling                           | 82       |

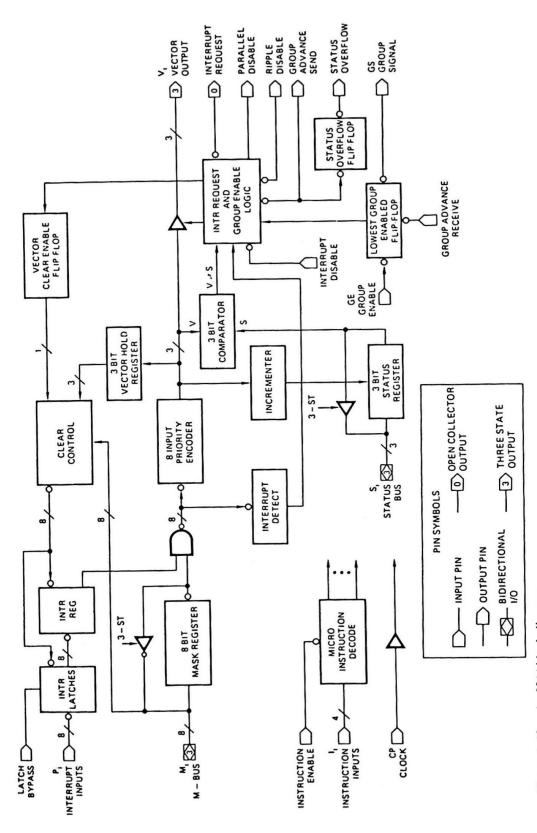

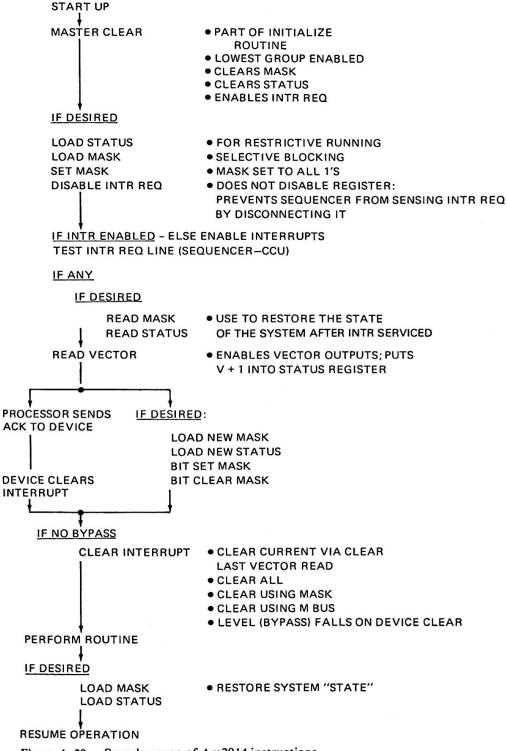

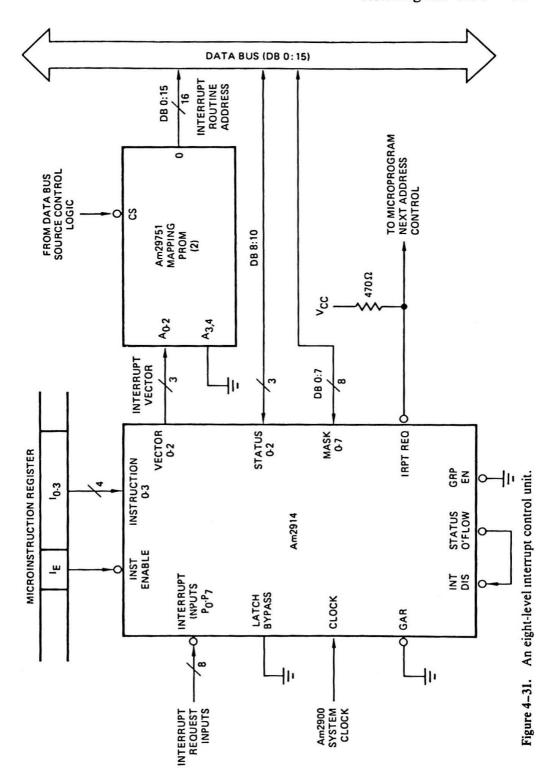

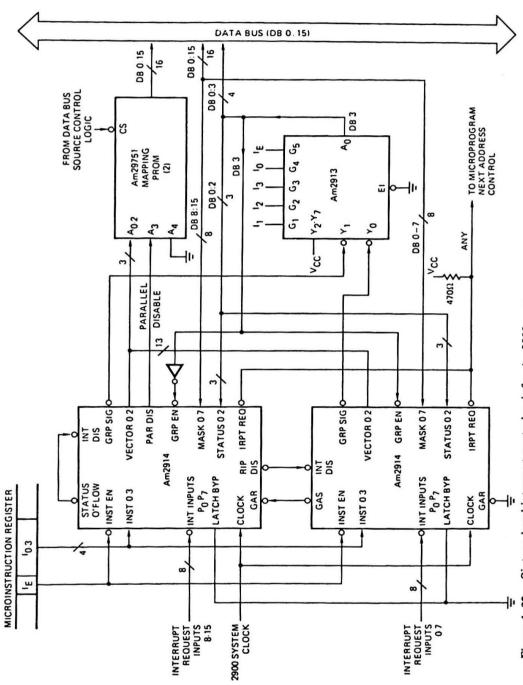

|   | Am2914                                       | 85       |

|   | Interconnection of the Am2914                | 85       |

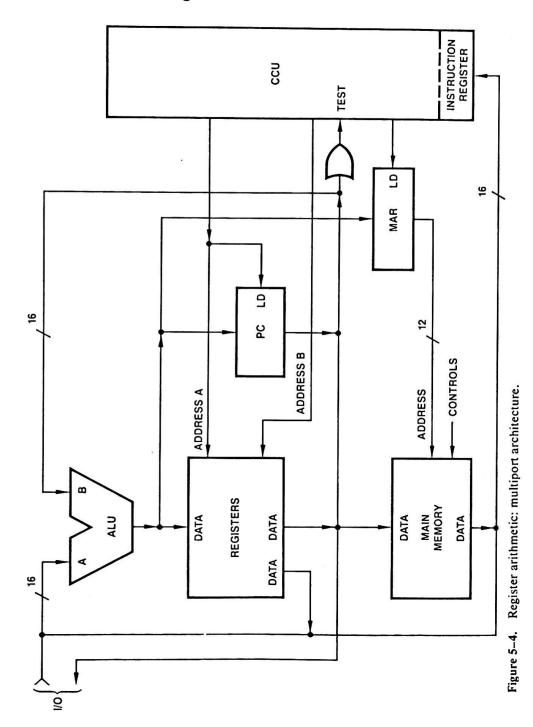

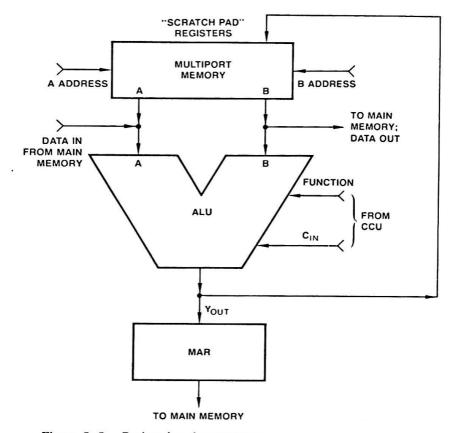

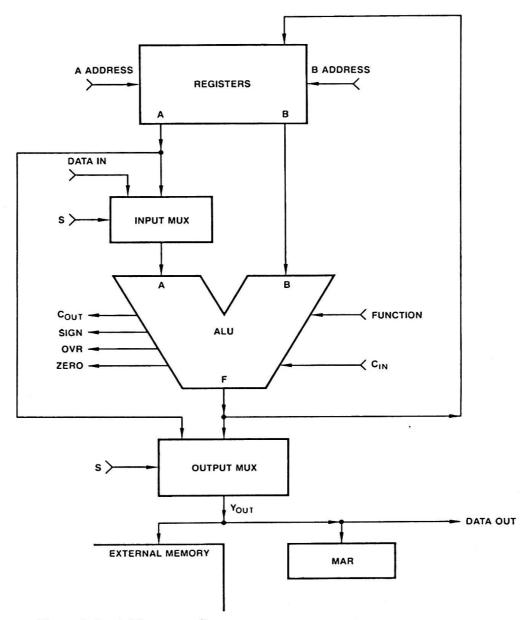

| 5 | Evolution of the ALU                         | 97       |

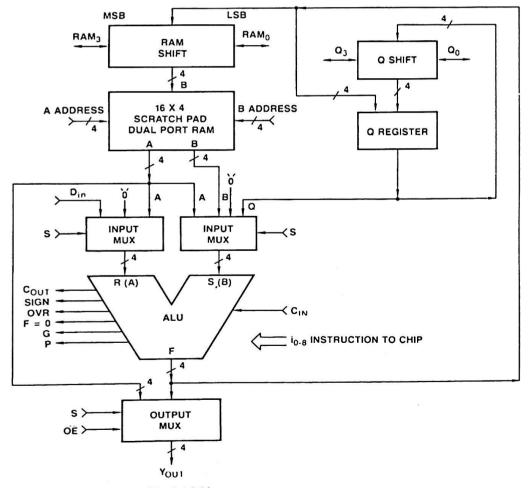

|   | Instruction Formats                          | 97       |

|   | Control Unit Function                        | 98       |

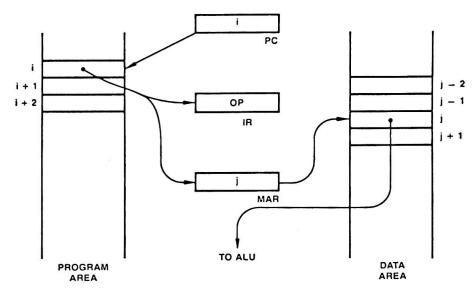

|   | PC and MAR                                   | 99       |

|   | Improving ALU Speed                          | 101      |

|   | Adding Flexibility                           | 105      |

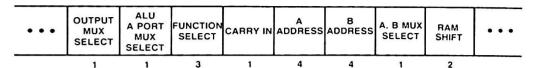

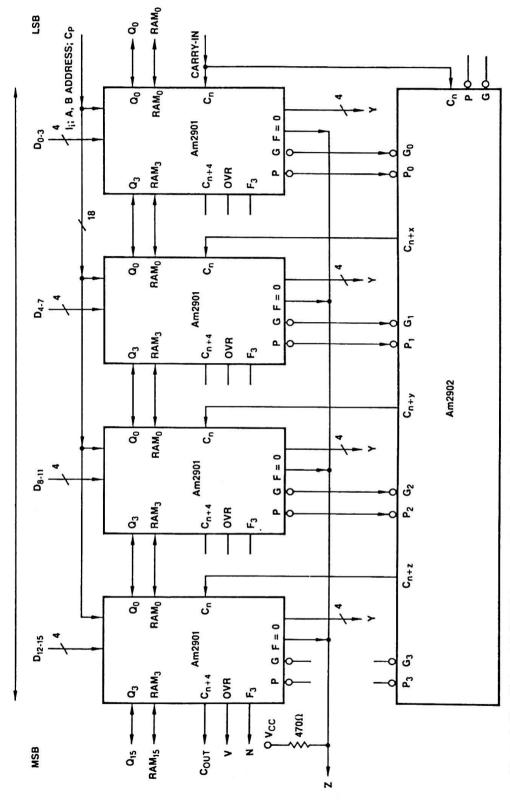

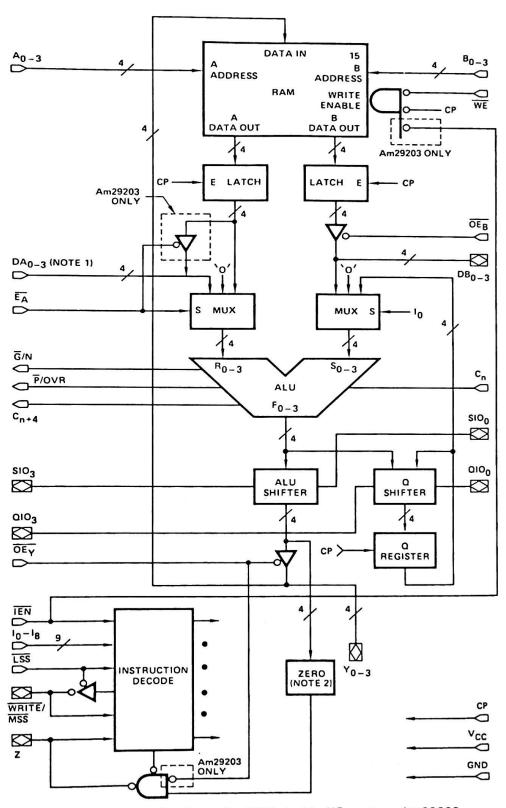

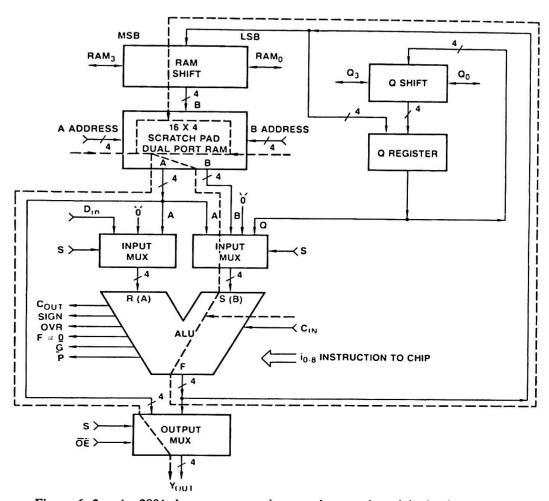

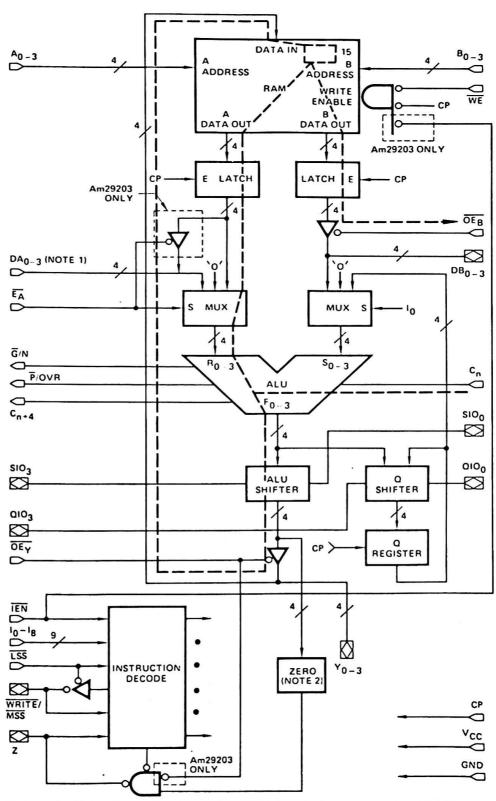

|   | Am2901                                       | 111      |

| 6 | The ALU and Basic Arithmetic                 | 117      |

|   | Further Enhancements                         | 117      |

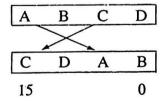

|   | Instruction Fields                           | 121      |

|   | Instruction Set Extensions                   | 121      |

|   | Sample Operations                            | 122      |

|   | Arithmetic—General                           | 125      |

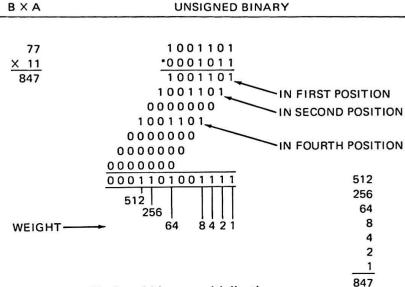

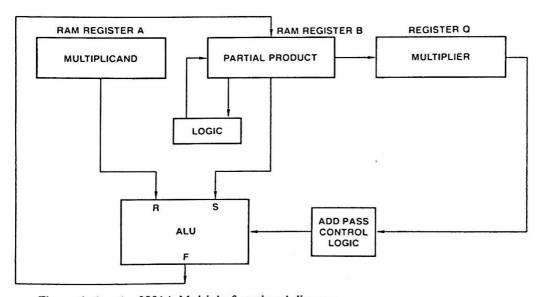

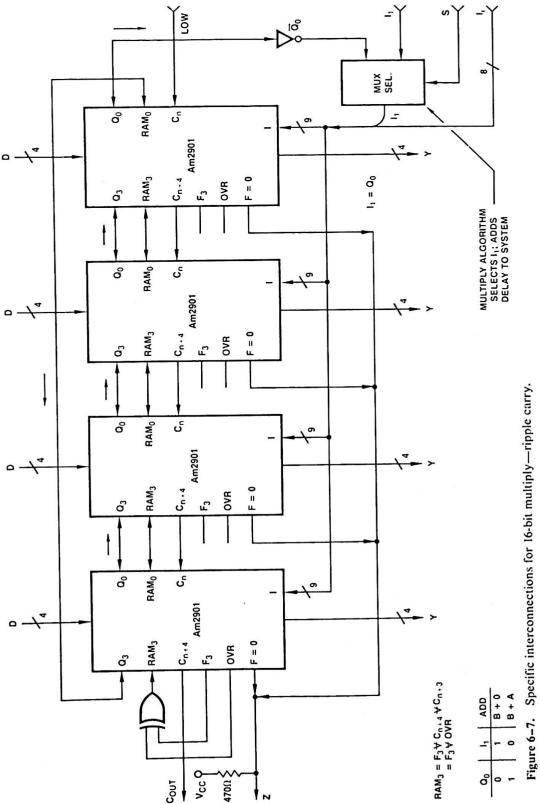

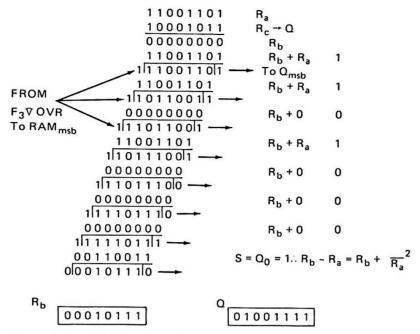

|   | Multiplication with the Am2901               | 129      |

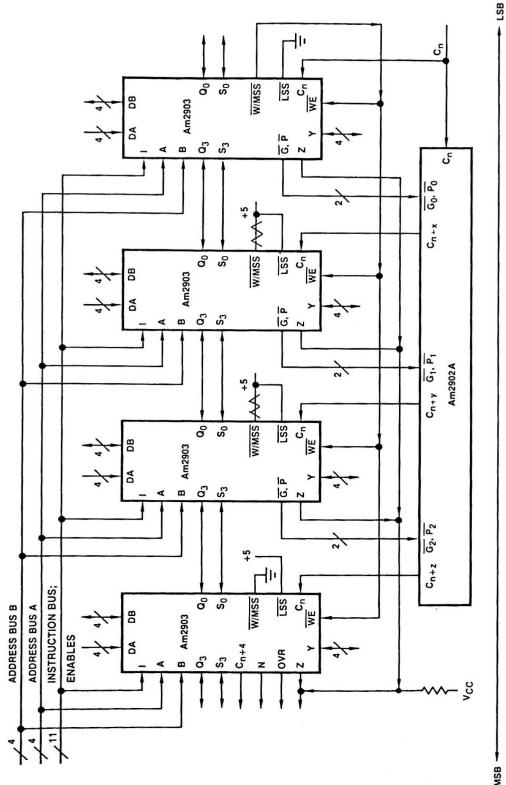

|   | Am2903 Multiply                              | 131      |

|    |                                | Contents | vii |

|----|--------------------------------|----------|-----|

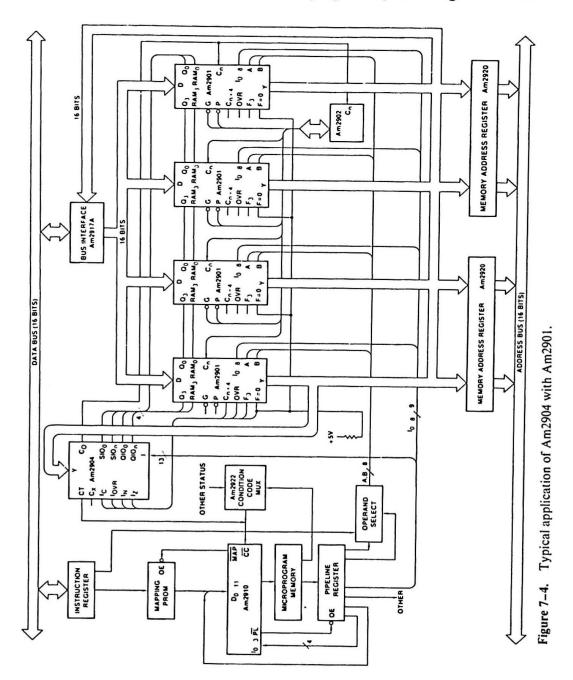

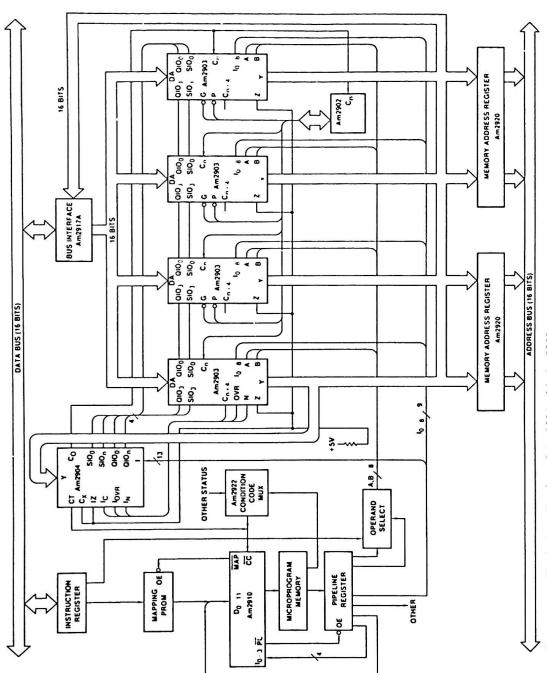

| 7  | Tying the System Together      | 1        | 133 |

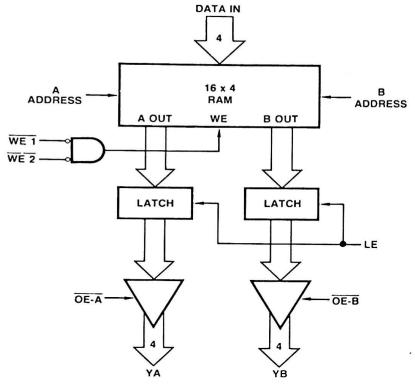

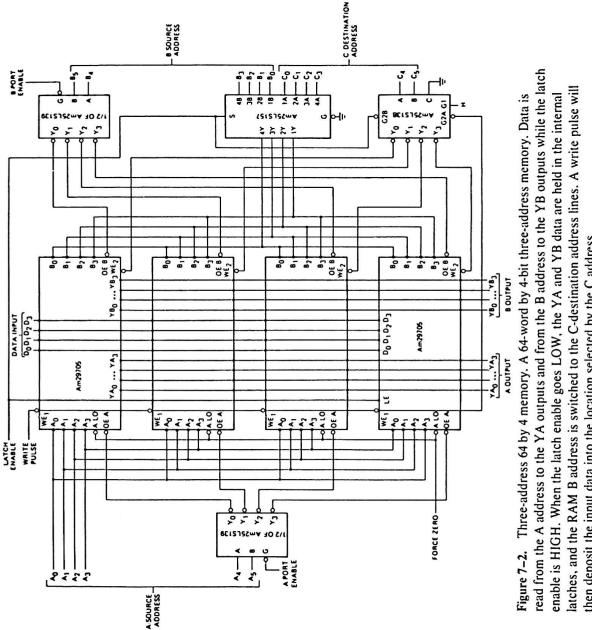

|    | Expanded Memory for the Am2903 | Ī        | 33  |

|    | MUX Requirements               | 1        | 33  |

|    | Status Register                | 1        | 36  |

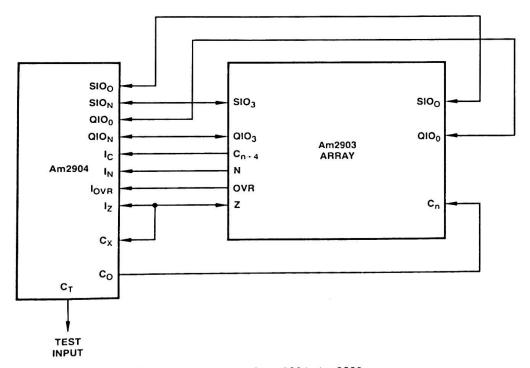

|    | Am2904                         | I        | 36  |

| ~. |                                |          |     |

| G  | lossary                        | 1        | 141 |

| In | dex                            | 1        | 145 |

# Preface.

This text has been compiled from the current and highly popular Customer Education Seminar, ED2900A, "Introduction to the Am2900 Family," offered by Advanced Micro Devices. No attempt was made to duplicate all of the material presented in the customer seminar. The intent was instead to present a true "introduction" for the undergraduate hardware or software student that could be covered in one quarter or semester. The ED2900A seminar assumes that the attendee either has a background in assembly level programming or has a background in SSI/MSI design. This text also makes this assumption.

The flow is an orderly evolution of a CCU design, adding one functional block at a time. The material is presented in a dual approach, referring to both the hardware and the firmware, or the software impact, as each feature is discussed.

The controllers are presented first, followed by the RALUs and their support chips. Interrupts are presented in two sections broken down by the hardware evolution. The final chapter provides a "typical" configuration of an Am2900 state-machine architecture CPU.

Chapter 1 is an introduction to the reasons why microprogramming should be selected as the means of implementing a control unit. This chapter also presents a discussion of language interrelationships covering topics from the typing of the conventional programmer languages to the functioning of the hardware through the microprogram. The basic concept of what a control unit does is described using a primitive CCU (computer control unit). The 2900 Family is also introduced and this bipolar bit-slice family will be used throughout the text. The concepts, however, apply to *any* microprogrammable system.

Chapter 2 begins the design evolution of a controller and introduces timing considerations. The hardware-firmware duality of the design decisions are stressed. In relation to the CCU used as an example, the concept of a mapping PROM is introduced. Only PROMs are discussed, although DEMUX networks, gate arrays, and PLA (programmable logic array) and PLA-type logic units are often used to perform the decode operation. Microprogram memory (control memory) is also presented. PROMs are referred to throughout the text although ROMs, PROMs, EPROMs, WCS (writeable control storage), and even parts of main memory may serve as the control memory. Only single-level control memory is referred to in the text although some designs exist which use two-level control stores (nanoprogramming).

Chapter 3 continues the evolution of the controller adding subroutines, nested subroutines, loops, and case statements to the tools available to the microprogrammer. The concept of overlapping field definitions in a microinstruction is introduced in relation to the branch-address and counter-value fields. This is an elementary form of variable formatting, the use of which should be minimized for clarity. The controller evolution leads to the microprogrammable sequencers—the Am2909 and Am2911—and the next address control block, the Am29811. (The letters A or B following a chip identification refers to the latest version available and may vary over time.) The various versions are pin-compatible and differ usually in die size and speed.

The case statement introduces the Am29803A, a device which assists in implementing up to a 16-way branch.

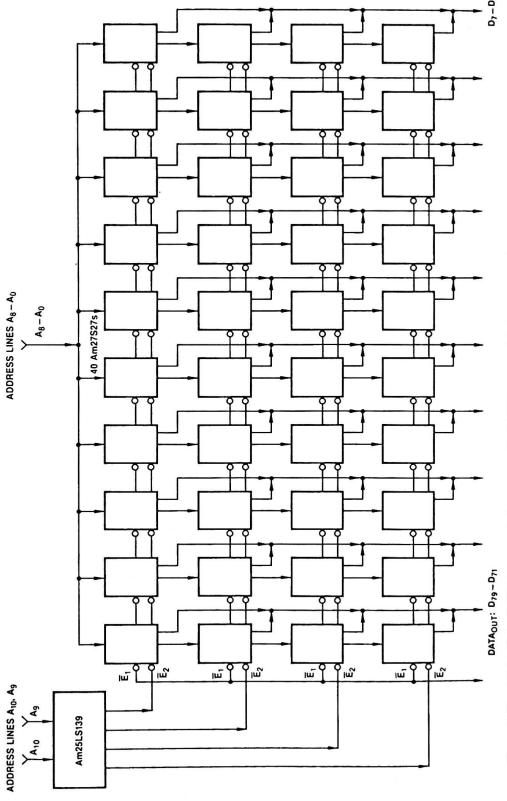

Microprogram memory implementation is briefly discussed, introducing the use of the Am27S27 registered PROM, dc and ac loading, and the effects on sequencer timing of excessive capacitive load.

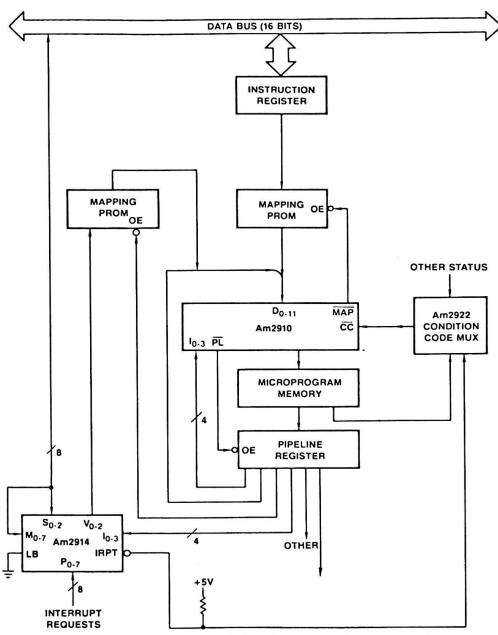

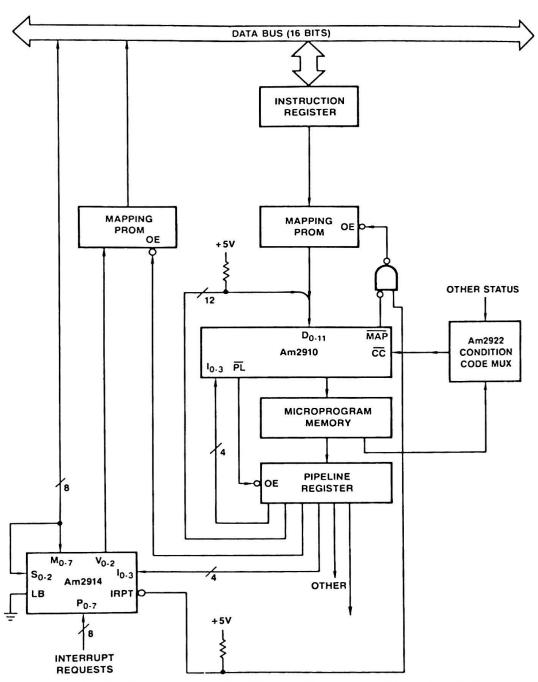

Chapter 4 continues the evolution of the CCU, introducing interrupt handling (the interrupt controller is discussed later). The interrupts are introduced here to demonstrate the  $\overline{OE}_{VECT}$  requirement of the next address control block. The evolution finishes with a detailed discussion of the Am2910 instructions. The instructions are discussed in their conventional usage. A number of instruction set variations are possible by tying control lines to different instruction lines ( $\overline{CCEN}$  to  $I_3$ , for example) and by ignoring the  $\overline{PL}$ ,  $\overline{VECT}$ , and  $\overline{MAP}$  outputs of the Am2910 and driving the output enables of these devices from the pipe-

line register (microinstruction) itself. The Am2914 interrupt controller is covered briefly.

Chapter 5 covers the RALUs—the Am2901 and Am2903—in a series of evolving steps as were the microsequencers. Every conceivable consideration cannot be discussed here, but enough is presented to cover the architecture of the Am2901.

Chapter 6 covers some basic operations and presents their microcodes to demonstrate microcode selection for these devices. Two's complement multiply is covered in some detail to highlight the differences between the Am2901 and the Am2903.

Chapter 7 describes the "typical" CPU as suggested by Advanced Micro Devices for the "typical" user. It covers the Am29705 two-port RAM and the Am2904 "LSI Glue" multiplexer-register support chip.

An instructor's manual of exercises and solutions has been prepared and is available from Advanced Micro Devices.

Although the text is original, many of the drawings have appeared in application notes and data sheets previously published by Advanced Micro Devices and are reproduced with the permission of Advanced Micro Devices. Those application notes written by the Bipolar Applications Department have served as the principal reference material. Principal authors of these notes, to whom I am indebted for their assistance and advice are:

John Mick, Engineering Manager, Systems and Applications, Digital Bipolar Products.

the late Michael Economidis, Section Manager, Systems and Applications, Bipolar Memory and Programmable Logic, Mr. Economidis was an expert on the Am2914.

Jim Brick, Applications Engineer, Bipolar Microprocessors Vernon Coleman, Senior Applications Engineer, Systems and Applications, Bipolar Microprocessor Circuit Definition.

William Harmon, Manager, Systems and Applications, Bipolar Microprocessing.

# Introduction

Over the years, there has been an evolution of the universal building blocks used by logic circuit designers. In the mid-1960s, there were SSI gates; NAND, NOR, EXOR, and NOT or INVERT. In the early 1970s, MSI blocks, registers, decoders, multiplexers, and others made their appearances. In the late 1970s, ALUs (arithmetic logic units) with onboard scratchpad registers, interrupt controllers, microprogram sequencers, ROMs/PROMs, and other LSI devices up to and including a complete one-chip microprocessor (control, ALU, and registers) became readily available.

SSI (small scale integration) is defined here to include chips containing approximately 2–10 gates. MSI (medium scale integration) is used for chips containing 20–100 gates. LSI (large scale integration) chips contain 200–1000 gates, with the upper limit continually extending as VLSI (very large scale integration) becomes a reality. The AmZ8000 CPU contains 17.5K gates; the M68,000 claims to contain 68,000 transistors.

## Selection of the Implementation

Today, a designer is faced with three basic choices in implementation: (1) SSI/MSI hardwired logic; (2) 9080A/8080A (8-bit) or AmZ8000-In8086-M68000 (16-bit) MOS fixed instruction set (FIS) microproces-

#### 2 Bit-Slice Design

sor; or (3) microprogrammable bit-slice architecture with the 2900 Family or other similar family. There are a number of factors which influence the decision as to which implementation is best for the application.

#### Architecture

In terms of the design architecture, any FIS MOS microprocessor by definition has its own predefined internal architecture, and this constrains the design options available. This fact is acceptable if the architecture provided by the selected MOS device satisfies the one desired for the application. An SSI/MSI implementation allows the designer to specify in complete, exact detail the architecture desired. With bit-slice devices, some constraints are placed on the designer, but most of the system architecture is left to user definition via the selected interconnections and the microprogram.

#### Size

The real estate or board space (rack space, etc.) is often of concern in a design because of space limitations. An FIS MOS microprocessor may use 3-6 chips for a typical average control system, versus 100-500 chips for the same system implemented in SSI/MSI and 30-60 chips for a compromise bit-slice design.

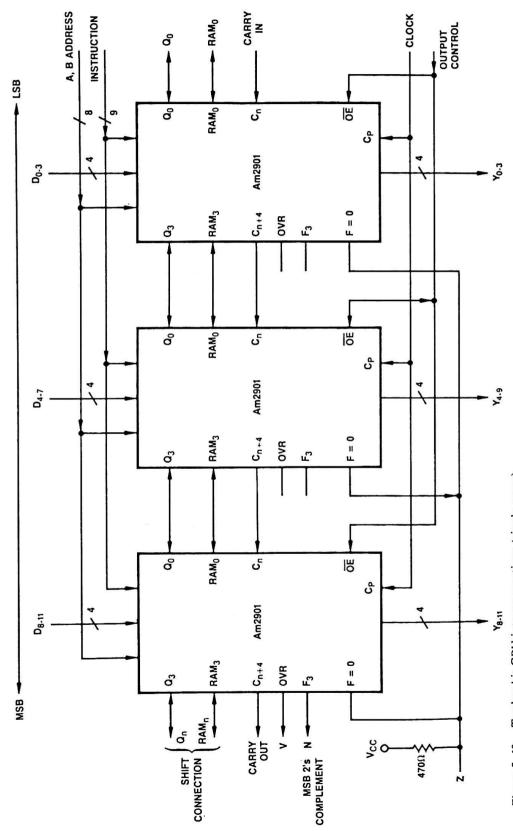

#### Word Length

The word length necessary for the system, whether a computer, controller, signal processor, or whatever, is usually known in advance. FIS MOS microprocessors can be used where their word length is compatible with the design objective. MOS devices exist for 4-, 8-, and 16-bit data word systems. Using SSI/MSI, any word length may be accommodated. Using bit-slice (the 2900 Family is expandable in multiples of 4 bits), a wide variety of useful word size systems are possible. When bit-slice does not conveniently match, SSI/MSI can be used to "patch" the basic bit-slice design.

#### Instruction Set

The instruction set that the system under design is to support has a major impact on the choice of implementation. The high dollar investment in software, which currently exceeds the hardware investments with a ratio as high as 10 to 1, often results in the prime directive of software compatibility: the new design *must* support the existing instruction set. FIS MOS microprocessors have a fixed instruction set. If there is an MOS microprocessor whose instruction set supports the design instruction set, then a microprocessor-based design can be

used. The current FIS microprocessors support assembly level languages and have software to support BASIC, PL/1, FORTRAN, PASCAL, and even COBOL. If the design has an unusual instruction set requirement, it would require that a program written in the desired instruction set be passed through an additional software process prior to actual MOS device execution.

The two most widely known 16-bit devices are the In8086, with its 8080-based architecture and instruction set, and the AmZ8000, with a general-register architecture and an instruction set based on the IBM SYS/370 and the DEC PDP 11/45.

An SSI/MSI design can be customed tailored to support any desired instruction set. A bit-slice design can be microprogrammed to support any desired instruction set. The principal difference between these two approaches is that one is done exclusively in hardware and the other (bit-slice) is done in hardware and firmware.

#### Speed

Another design criterion or specification is the required speed of the design. SSI/MSI using Schottky TTL and bit-slice (2900 Family) can support systems with 125 ns cycle times. MOS microprocessors are slower, with approximate cycle times of  $1-2~\mu s$ . The newer MOS devices support 4-5~MHz clock speeds. The newer bit-slice devices are targeted for 100 ns microcycle systems. When instruction times are given for an MOS microprocessor, the instruction is a machine level instruction. To properly compare this with bit-slice or SSI/MSI, macro instruction execution times must be used where a macroinstruction is a machine instruction which the microprogram supports. Bit-slice designs exist with effective macroinstruction times of 320 ns (HEX-29) and 200 ns (SUPER-16) for register-register operations (Chapters 8 and 9 of AMD's Bit-Slice Microprocessor Design Series).

#### Tradeoffs

Design tradeoffs are summarized in Table 1-1. Basically, where high speed, long word lengths, or critical instruction sets occur, MOS FIS cannot be used. If design time-parts count-board space restrictions also exist, or if production volume does not support the effort required to do an SSI/MSI design (considered the most difficult to do correctly), the bit-slice devices are the best choice. It should also be noted that a microprogrammed bit-slice design is upgraded or changed, usually through a change of PROM or a reload or patch of writable control store, more readily than is a hardwired SSI/MSI design.

Bit slice devices are applied to three basic areas: machines with long words, machines with special instruction sets, and high-speed

Table 1-1 Design Tradeoffs

|                            |                                   |                                    | FIS MOS                         |

|----------------------------|-----------------------------------|------------------------------------|---------------------------------|

|                            | SSI/MSI                           | Bit-Slice Devices                  | Microprocessor                  |

| Architecture               | Any Desired                       | Pseudoflexible                     | Predesigned                     |

| Physical size<br>(typical) | 500 chips                         | 50                                 | 3–6                             |

| Word length                | Any Desired                       | Multiples of 2, 4                  | 4, 8, 16                        |

| Instruction set            | Any desired; May<br>be wired      | Any desired may be microprogrammed | Constrained if speed a problem  |

| Speed                      | 100-200 ns                        | 100-200 ns                         | 1–2 μs                          |

| Design time                | Long, slow, if done<br>correctly  | Fast                               | Fast                            |

| Debug                      | Difficult                         | Development systems aid process    | Development systems aid process |

| Documentation              | Tedious, often<br>outdated        | Forced via<br>microprogram         | Software is major portion       |

| Upgrades                   | Up to a full<br>redesign required | Easily done, can be preplanned     | Easily done                     |

| Cost                       | Highest                           | Medium range                       | Lowest                          |

machines. The best examples are signal processors, with a low volume per particular specification and which require high speed and a long data word, and emulators such as the one for the SIGMA 9 (32-bit word) and the one for the GE 400 (24-bit word), where software compatibility to the existing system at increased throughput is mandatory. Variable instruction set minicomputers have also been developed using bit-slice which allow custom-tailored instruction sets to be microprogrammed around one fixed hardware implementation.

#### Microprogramming

Microprogramming is to hardware design what structured programming is to software design. If a bipolar (Schottky TTL) machine is to be built, in bit-slice or in SSI/MSI, its control should be microprogrammed. First suggested by Wilkes as a methodical way of handling the control unit of a system, it is now recognized as the best approach. Why?

First, random sequential logic circuits are replaced by memory (writable control store or ROM [read-only memory] or PROM [programmable ROM] or related devices). This results in or forces a more structured organization on the design.

Second, when a unit is to be upgraded, a field engineer can replace the appropriate PROM considerably easier than hardwiring and patching new components onto a crowded printed circuit board (PCB) with all of the associated pitfalls of such activity.

Third, an initial design can be done such that several variations exist simply by substituting one or more PROMs (changing the microprogram), and enhanced versions can be preplanned such that version B is constructed by simply adding a PROM or two to version A, simplifying production. The basic units would contain sparsely populated PCBs with upgrades provided for in the etch and connections. In these cases, simply adding PROMs (and changing others as required) expands the system. This technique is also commonly used for RAM memory (read-write memory) expansion.

The microprogram, documented in the definition file and in the assembly source file, serves as the principle documentation of the firmware. This, coupled with the modularity of the design as enforced by the use of microprogram control, provides a better opportunity for clearer documentation than multipaged schematics can provide.

Last, diagnostic routines can be included in the PROMs supplied with the final system and can be called in by a field engineer through a test panel and executed to aid debug. Some diagnostic routines could be microprogrammed into the system such that they are routinely executed in the normal running environment. For more severe testing, the

normal PROM memory could be swapped with a special test memory simply by substituting PROMs.

#### Advantages of LSI

If bipolar has been chosen over MOS because of speed, LSI is preferable to SSI/MSI for several reasons.

First, costs are reduced. LSI requires fewer parts and therefore fewer boards and less rack space. There is less etch and fewer pin connections with LSI as more and more of the connections are moved inside the package.

Second, using LSI improves reliability. Approximately 80% of the failures of working systems are caused by broken etch or by bent pins and other broken external connections. Using SSI/MSI, a typical controller might use 300 16-pin DIPs, for a total of 4800 pins. The same controller done with LSI might use 30 40-pin DIPs, for a 1200 pin total; the other connections having been moved inside of the package.

The 2900 Family is going to be introduced in this text. It is a design rule that every design should use industry-standard parts. The Am2900 family is considered to be the industry standard for bipolar bit-slice devices. It is a microprogrammable family of LSI-level complexity. Table 1-2 summarizes its advantages.

## The Am2900 Family

The 2900 Family components include or will soon include (1) CPU-ALU and scratchpad register units: Am2901, Am2903, and the new Am29203; (2) microprogram sequencers and controllers: Am2909/2911 and Am2910; (3) bipolar memory: various devices, including error detection and correction controllers and support devices (Am2960 Series); (4) interrupt controller and support devices: Am2914, Am2913, and Am2902; (5) bus I/O: Am2950 and support devices; (6) DMA sup-

**Table 1–2** Microprogramming with LSI—Advantages

More structured organization

Field changes—may be as simple as replacing a PROM

Adaptions—may be as simple as replacing a PROM

Expansions—preplanned, may be as simple as adding a PROM

Better documentation

Hardware and firmware can be designed in parallel

LSI uses fewer parts

LSI has better reliability

Diagnostic PROM can aid debug, maintenance

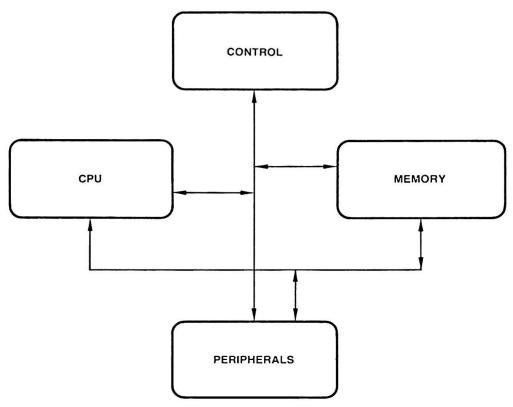

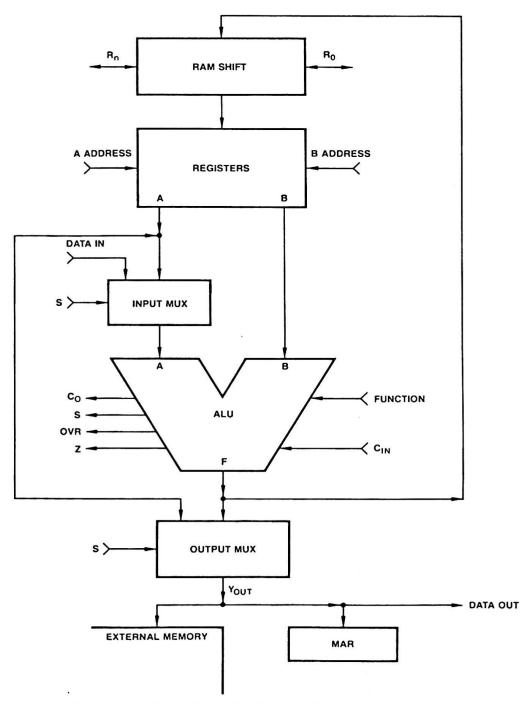

Figure 1-1. Simplex system block diagram.

port: Am2940 and Am2942; (7) timing support via microprogrammable microcycles: Am2925; (8) main memory program control: Am2930 and Am2932; and (9) the new 16-bit Am29116.

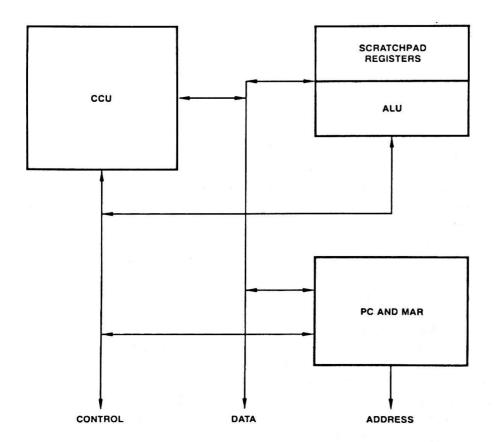

Consider a simplex block diagram of a basic computer, shown in Figure 1-1. The essential blocks of this diagram are (1) the CPU (central processing unit), containing the ALU and scratchpad registers, the PC (program counter), and MAR (memory address register); (2) the main memory, where active programs and data are stored; (3) peripherals, including backup memory, input, and output; and (4) the CCU (computer control unit), which supervises everything else and contains the control logic instruction decode and the PROMs. The CPU is where data is processed; the CCU is where instructions are processed.

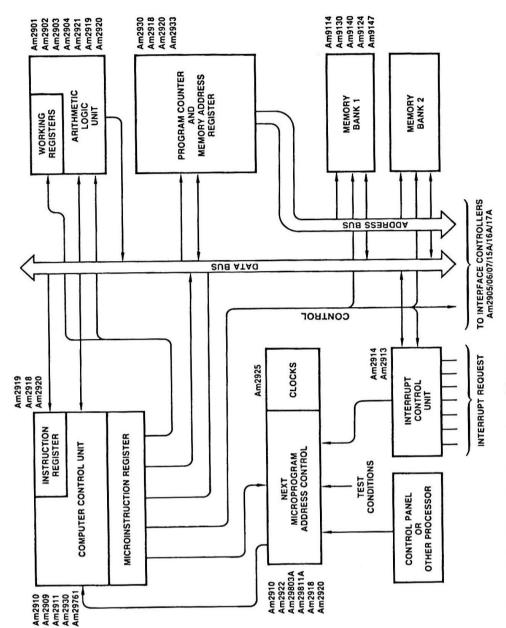

From this simple overview, progress to Figure 1-2 and the generalized computer architecture blocked out to show the various members of the 2900 Family and their applications.

## Language Interrelationships

Programming classes relate source code—written by the user in some programming language—to object code—the machine level, machine-

Figure 1-2. Generalized computer architecture.

executable instructions—via an assembler or compiler. A compiler is a software program that translates a high-level (compiler level) language program into object code. An assembler is a software program that translates an assembly level source program into object code. There are usually several compilers and one assembler per computer system.

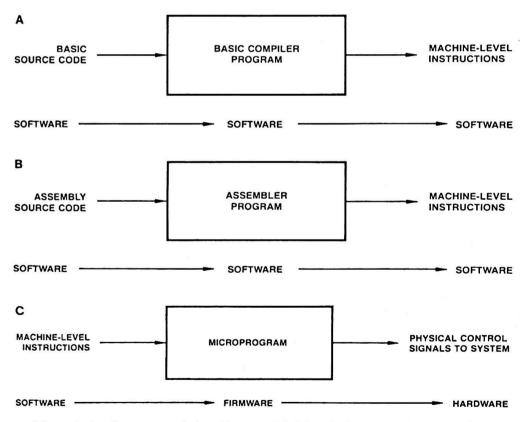

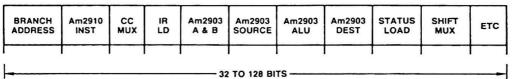

Compilers translate at an average ratio of four to one (four machine instructions per source instruction [FORTRAN IV]) or higher (six to one for FORTRAN VI). Assemblers can be very nearly one to one, with assembly statements being a mnemonic form of the bit pattern machine instruction. In both cases, software is processed by software to produce software, as shown in Figure 1-3.

#### High-Level Language

High-level languages are fairly free format, i.e., they have few columnar placement restrictions on the coding form, use pseudo-English mnemonics, and have prewritten functions. Their capabilities include arrays, loops, branches, and subroutines, with the current emphasis on structured programming tools, such as IF-THEN-ELSE, CASE, and PROCEDURE statements.

Figure 1-3. Language relationships. (A) High level. (B) Assembly level. (C) Micro level.

#### Assembly Level Language

Assembly level languages have a more restricted format, require a precise data definition, may involve the programmer in program placement in memory, and use mnemonics for instructions but have more of them. Most instructions or statements are restricted to one operation—hence the approximate one to one translation ratio. The assembly level programmer in general must know more about the machine being used than the programmer who writes in FORTRAN or BASIC.

#### Machine Level Language

Machine level languages are the closest to the system of the software level languages. They are usually written using an encoding of instructions, data, and addresses in either octal or hexadecimal notation, are more tedious to construct and debug, and are more restrictive in the format required than the assembly level languages. They can require more specific detail from the programmer, depending on the complexity of the system being programmed.

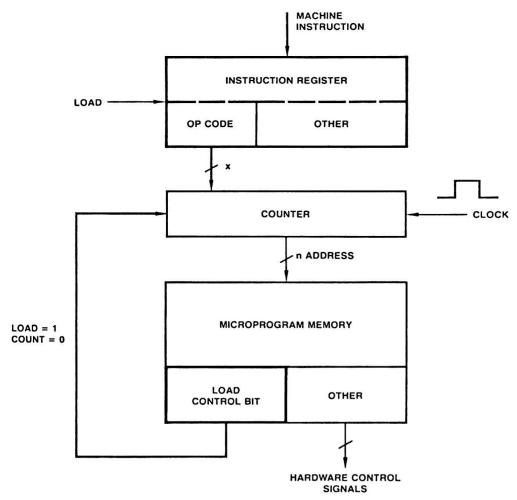

#### Microprogramming

The machine level instructions are what the computer control unit (the CCU) receives. In a microprogrammed machine, each machine level instruction (referred to as a macroinstruction) is decoded and a microroutine is addressed which, as it executes, sends the required physical control signals in their proper sequence to the rest of the system. This is where the software instruction via a firmware microprogram is converted into hardware activity.

## Microprogram Storage

The various software programs will vary from hour to hour, or more often, and their data will vary; therefore read-write or RAM memory is required as their storage area. The microprogram, however, will usually remain the same. There are a few machines—the Burroughs 1700, for example—that load a different microprogram for each of several application languages.

Where one microprogram is to be used by the system, ROMs (high production) or PROMs (lower production, prototype) are used for the microprogram memory. Such systems are called microprogrammed systems.

When a microprogram may be replaced by another, for example, to emulate another machine or to do a diagnostic run, then either a separate read—write memory, called a writable control store (WCS), or part of the system main memory is used as the microprogram memory with minifloppies, tape cartridges, or an area of main memory as the auxiliary storage for the microprograms. This alterability is attractive for

special application systems such as experimentation control. Writable control storage is also useful for prototype systems and is present in development systems for flexibility. Systems with alterable microprograms are called microprogrammable systems.

Throughout the remainder of the text, the microprogram control memory will be assumed to be a PROM memory for the sake of simplicity.

#### **Format**

Each machine level instruction is in the form of an op code and operands. There may be several different formats for the instructions in any one machine. These instructions are decoded by the control unit, and the decoding produces an address which is used to access the microprogram memory.

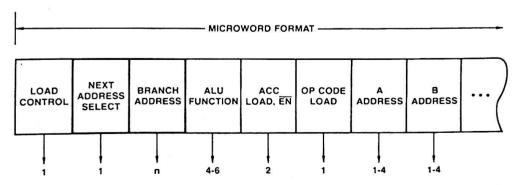

The microroutine for the individual machine or macroinstruction is called into execution and may be one or more microinstructions in length. (A microinstruction will be assumed to execute in one microcycle; such a microinstruction is also called a microstep.) Each microinstruction contains information blocked out in fields, where each microinstruction field directs or controls one or more specific hardware elements in the system. Every time that a particular machine instruction occurs the same microroutine is executed. The particular sequencing of the available microroutines constitutes the execution of a specific program.

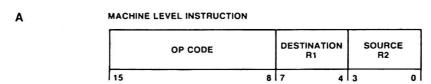

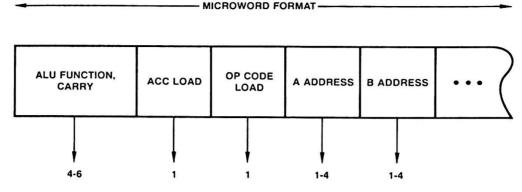

Machine level language is very close to the hardware and has a very constrained format. It uses no mnemonics and requires that everything be specified by the programmer, including program address and data addresses. A sample machine instruction format is shown in Figure 1-4A. More than one machine instruction format usually exists for a given system.

# B MICROPROGRAM INSTRUCTION

Figure 1-4. Sample formats. (A) Sample machine level instruction (register addressing). (B) Sample microprogram instruction (Am2900 family). (Addr., address; CC, condition code test; Dest., destination; Inst., instruction; n, unknown number of bits; R1 and R2 are operands.)

Microprogramming is done in the format or formats designed by the programmer. Once chosen, it (or they) becomes fixed. Each field controls a specific hardware unit or units, and the possible bit patterns for each field are determined by the signals required by the hardware units controlled. Simple, short microprograms can be recorded in bit string fashion and prototype PROMs created using manually operated PROM burners. A sample microinstruction format is shown in Figure 1-4B. More than one microinstruction format may exist for a given microprogram.

#### **Development Systems**

Longer microprograms (> 32 microwords in length or with microwords > 16 bits wide) are better handled with development systems. These systems allow each field to be defined with mnemonics, which is a documentation aide. (Labels such as ON, OFF mean more to a human than 0, 1.) Once the fields are defined, the microcode (microprogram, microroutines, microinstructions) can be written in mnemonics, more or less as a pseudoassembly language, providing human-readable documentation in the process. The development system then may be used to assemble the microprogram thus written and to create the input to an automated PROM burner.

The development systems allow prototype hardware to be connected to them, and with the prototype microprogram loaded into the writable control store of the development system the development system can be used to debug hardware and firmware in parallel. The WCS is used to replace the microprogram control store of the prototype system. For the 2900 Family, the development system is Advanced Micro Computer's AmSYS 29™.

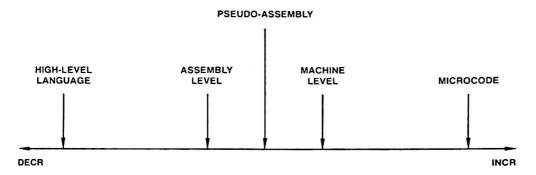

Microprogramming is the programming level that is closest to the hardware, and the microprogrammer must know everything about each of the pieces of hardware which are to be controlled. The tradeoff here is between the detail level of the programming and the power and the control of the hardware that is possible. The actual number of microroutines required is a function of the number of machine level instructions that the system is to recognize. For an average computer control system, there would be about four microinstructions per machine instruction, with the minimum being 1 and the maximum 16. This varies dramatically with the application. Figure 1-5 gives the relative relationships between the ease of programming and the level of control provided by each of the language levels.

# Controller Design

A computer control unit (CCU) will be used for illustration throughout the text; the design approach, however, is applicable to any controller.

Figure 1-5. Language interrelationships: Requires (1) detailed knowledge of hardware; (2) time to write programs; (3) power and control of hardware.

#### A Simple Computer

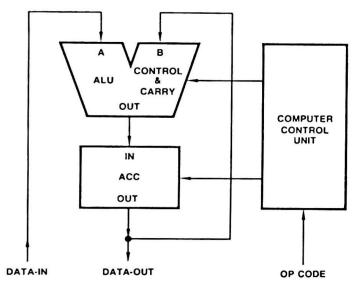

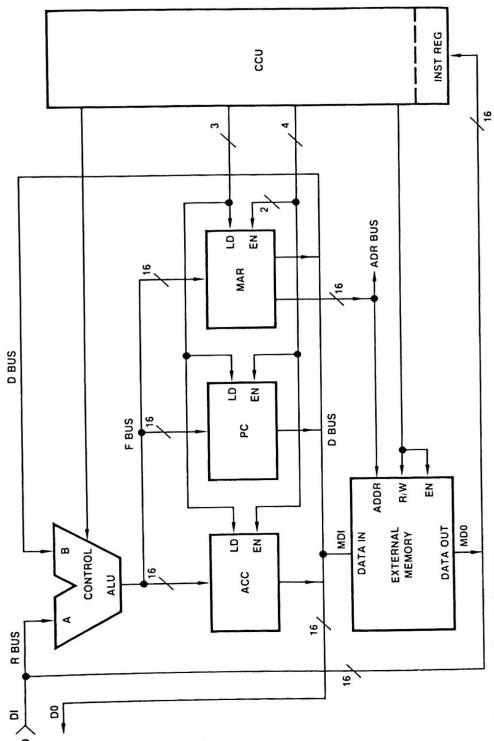

The simplex computer of Figure 1-1 is further reduced as shown in Figure 1-6, which shows (1) a CCU, (2) the ALU and scratchpad registers, (3) the PC (program counter), and (4) MAR (memory address register).

Figure 1-6. CPU and control block diagram.

Figure 1-7. Simple sequential system (simple computer/SIMCOM).

The MAR is the output to the address bus for peripheral and memory addressing. The CCU controls all devices shown and outputs to external devices via the control bus. The ALU receives and outputs data via the data bus. Addresses may be loaded into the PC via the data bus. This is a very elementary system.

This system is reduced further in Figure 1-7, where the CCU is shown to control the ALU and the ACC (accumulator, a register) with its other control functions ignored for now. Here the data may be input only via port A of the ALU; port B is loaded via the ACC register; and data is output only from the ACC. The CCU receives an instruction in the form of an op code *somehow* (ignore how for the moment). Given the op code as input, the CCU must proceed to generate (1) the appropriate function control signals (three to six bits would be typical); (2) the ACC load-enable controls (two bits); and (3) the carry-in  $(C_{in})$  bit value. For this elementary unit the microword format might appear as shown in Figure 1-8.

A simple ALU could have three control lines and perform addition, subtraction, and the logical OR, AND, EXOR, and similar functions, up to a total of eight functions. The carry-in bit allows the three arithmetic functions A + B, A - B, and B - A to be varied to A + B + 1, A - B - 1, and B - A - 1. This simple ALU would support the machine level and assembly level instructions ADD, SUB, OR, AND, and EXOR, as shown in Figure 1-9.

Figure 1-8. Control required from CCU.

#### Constructing the CCU

Now that what the CCU must do—namely, translate the op code received into ALU-ACC controls—is defined, how is the CCU constructed?

#### Hardwired Design

As stated before, the CCU can be built from the traditional sequential circuit network, an SSI/MSI hardwired unit. The advantages and justifications of this approach are as follows:

It is a custom design.

It may be a more minimal (irredundant, testable) solution.

It is justified if the design is to remain rigid or fixed.

It may be the highest-speed implementation.

It is justified if a high volume is to be produced before redesign.

| CONTROL LINES  |                |    | ALU FU              | NCTION              |

|----------------|----------------|----|---------------------|---------------------|

| S <sub>2</sub> | S <sub>1</sub> | So | C <sub>IN</sub> = 0 | C <sub>IN</sub> = 1 |

| 0              | 0              | 0  | A + B               | A + B + 1           |

| 0              | 0              | 1  | B-A-1               | B-A                 |

| 0              | 1              | 0  | A-B-1               | А-В                 |

| 0              | 1              | 1  | AVB                 |                     |

| 1              | 0              | 0  | ΑΛB                 |                     |

| 1              | 0              | 1  | ΆΛB                 |                     |

| 1              | 1              | 0  | A₩B                 |                     |

| 1              | 1              | 1  | A¥B                 |                     |

|                |                |    |                     |                     |

Figure 1-9. ALU functions.

The disadvantages are as follows:

There is a lengthy design time.

Documentation is difficult to create and to maintain due to volume.

Minimization to remove redundancy is difficult, if done at all.

If minimization is not done, redundancy will interfere with testability.

Design changes require a partial or total redesign.

Debug is difficult, with races or hazards.

Board space is high.

Pin count is high (external connections).

Modularity and therefore structure is usually not present.

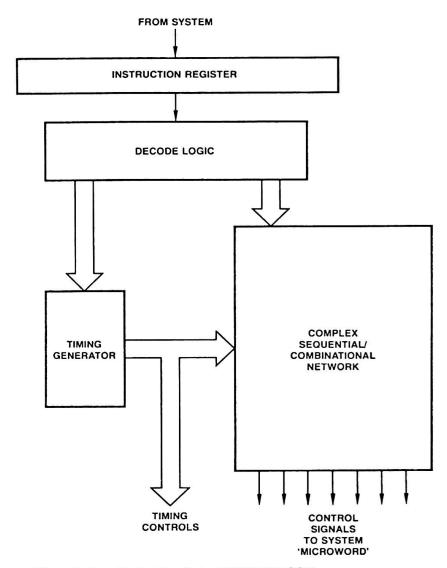

A hardwired control would consist of and instruction register (IR), decode logic, a timing generator network, and a complex sequential-combinational network. Output from the network would be the control signals for the rest of the system, as shown in Figure 1-10.

Microprogrammed Design

Assuming that the required speed has negated using MOS FIS microprocessors, the control can be done with microprogramming.

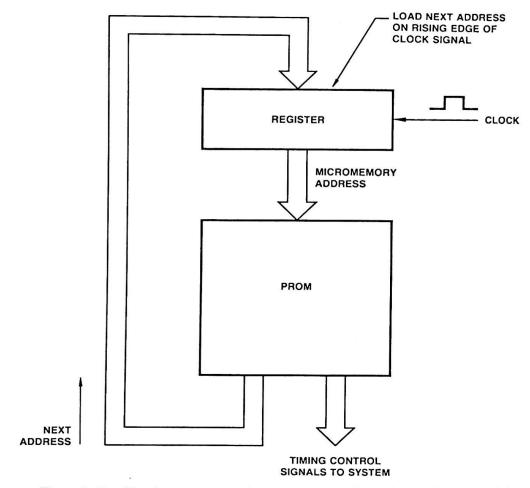

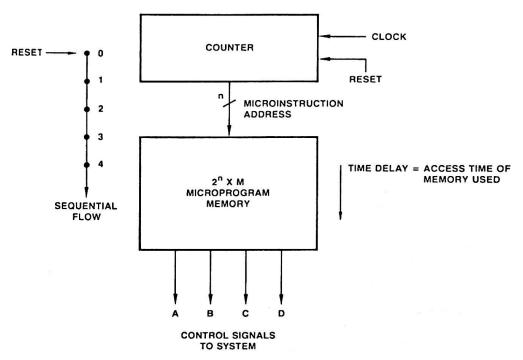

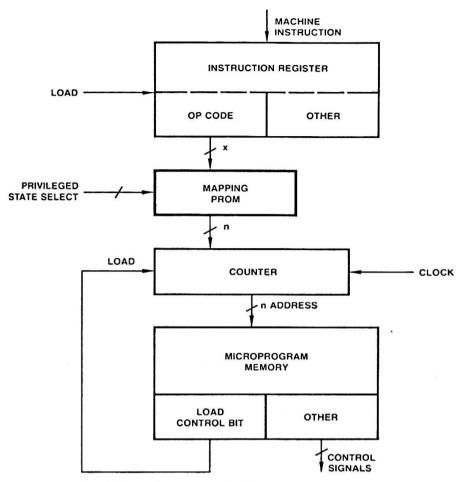

The simplest microprogrammed computer control unit would require an instruction register, decode logic, a clock source, and a ROM-or PROM-based control memory. Output from the control memory would include the control signals for the rest of the system. If a control unit other than a CCU is being developed, the unit could be as simple as a register, a clock source, and a PROM-based control memory, as presented in Figure 1-11.

The advantages of a microprogrammed approach to the construction of a control unit are as follows:

It is custom design at a higher level.

Microprogramming allows a systematic approach to the design.

The result is a compact, modular physical unit (compared to SSI/MSI).

The result is a flexible design (the unit can be microprogrammed to perform different control functions and different variations of those functions, in most cases without affecting the physical hardware).

If a proper structured programming approach is used to create the microprogram, there will be better documentation of system operation than is possible with a hardware-only design.

Diagnostic routines could be microprogrammed into the control memory itself or into special PROMs for use in troubleshooting the system.

There is a shorter design time compared to SSI/MSI.

Figure 1-10. Typical hardwired (SSI/MSI) CCU.

Design aids via development systems exist to support the above.

For a hardwired design, the design time goes up as people are added to a project above some critical number, such as two or three people. Microprogrammed design can use groups operating in parallel, since the microcode and hardware development can generally proceed in parallel.

#### Cost Effectiveness

The trend over time is for microprogramming to become the cost-effective method of control unit design at lower and lower levels of design complexity. The PDP-11 series of computers is a good example

Figure 1-11. Simplest control unit implementation. (Clock signal refers to the rising edge.)

of this trend. The PDP-11/20 was designed when hardwired logic was more cost effective for the level of "functionality" of the PDP-11; the PDP-11/60 was designed when microprogramming had become the more cost effective choice. The PDP-11/60 has more control functions implemented via microprogramming than does the PDP-11/20, although the "functionality" (design complexity) of the systems are considered to be approximately equal.

2

# Simple Controller

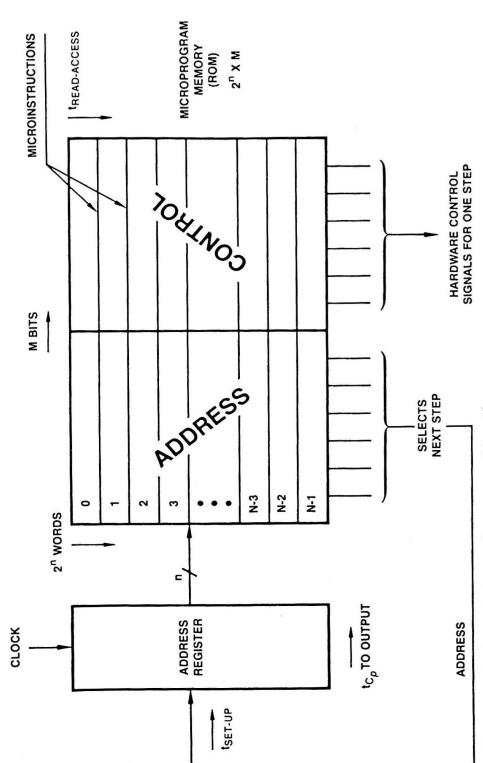

The very simplest microprogrammed controller is constructed from a PROM (assume that this means ROM or PROM from now on) and a register, as shown in Figure 2-1. The load enable on the register is connected to the clock signal. The register outputs an address to the PROM memory, and this address is used to fetch the next microinstruction that is to be executed. No next-address logic is included or required. After a time delay equal to that needed for stabilizing the register outputs plus the read access time of the memory, the memory outputs both the control signals to the rest of the system and the next address to be loaded into the register. The PROM memory is also referred to as the control memory. The output from the memory must be stable before the next clock pulse  $(C_p)$ :

$$\underline{C}_{p} = \overline{t}_{\text{read access}} + \overline{t}_{\text{register}} + \overline{t}_{\text{setup time}}$$

of memory

$$C_{p} \text{ to output} + \overline{t}_{\text{setup time}}$$

The size of the memory is  $2^n$  words, with each word M bits long. The M bits are formed from the C control bits plus the n address bits required to specify the next instruction:

$$M = C + n$$

Figure 2-1. The simplest implementation of a sequential machine.

word width equals the number of control bits plus the number of next-address bits.

The programmer is free to place microinstructions anywhere in any order as long as each one references the next executable address. This system will run from clock power up until clock power down. Assume on power up that the register is cleared and the first address executed is address 0. Since no next address logic is provided, only one sequence is possible. This controller is suitable for process control (repetitive looping of a sequence).

### **Sequential Execution**

A reduction in required PROM memory is possible by removing the requirement of the next-address field. This is reasonable because the microprogram can be loaded into PROM in its executed order as one long sequential routine, as diagrammed in Figure 2-2. In this case the next microinstruction address is always equal to the current microinstruction address plus 1.

The register is replaced by a counter, incremented by the clock and reset to zero on startup. The clock pulse width is determined by

$$\underline{C}_p = \overline{t}_{\text{read access}} + \overline{t}_{\text{counter } C_p \text{ to output}}$$

Figure 2-2. Sequential control.

#### 22 Bit-Slice Design

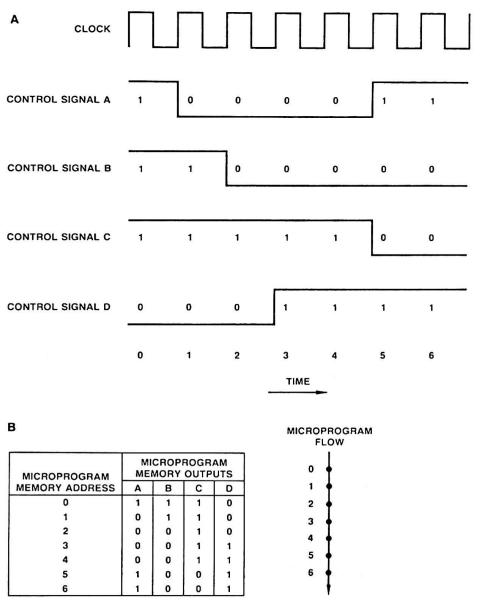

Figure 2-3. Sample sequential microcode. (A) Desired control. Assume that this is the desired control for some system. (B) Microcode and flow. This is then the microcode for sequential execution.

which is approximately the same as before, since

$$t_{\rm read\ access} >> t_{C_{\mu}}$$

to output

To derive the control portion of the microcode for either of the two control units described so far, assume a timing diagram exists. By digitizing the timing signals using the clock step and assuming all changes correspond to the rising edge of the clock, the microprogram

Figure 2-4. Multiple sequence controller. (A) Controller. (B) Microword format. (Load cont., load control)

control field is simply the binary word at each time slice. The procedure is shown in Figure 2-3.

# **Multiple Sequences**

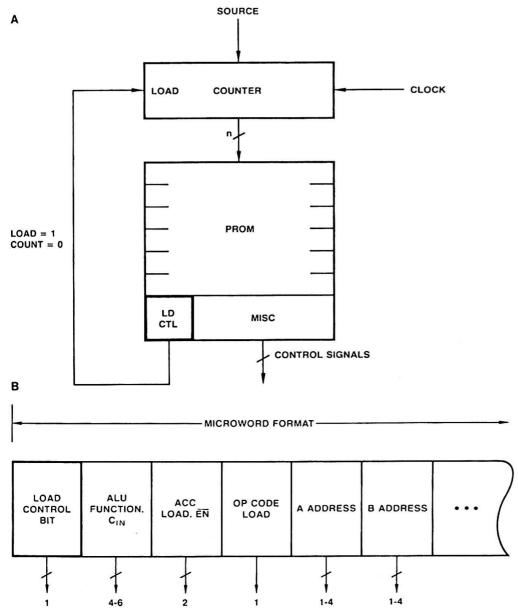

The controller may be made to execute several sequences by adding one control bit to the word width, the load control bit. This bit connects to the load control line of the loadable counter, as shown in Figure 2-4.

The data inputs to the counter receive the start address. The new start address is gated into the counter when the load control bit equals 1. The counter operates as a counter as long as the load control bit equals 0. Each microroutine or microinstruction sequence would contain a 1 in the load control field in the last microinstruction of the sequence only and a 0 in that field for all other microinstructions.

The size of the PROM memory is determined by the total number of microinstructions it must store. Since PROM memories come only in certain sizes, a "ballpark" number is sufficient for selection. The smallest sizes are 32 by 8 (nonregistered) and 512 by 18 (registered PROM). The number of address bits required and the size of the counter are determined by the amount of the memory that is used or that is anticipated to be used in later enhancements.

#### Start Addresses

If the controller is a CCU, the start address of each microroutine is derived from the current machine instruction. At the minimum, an instruction register must be added between the data bus and the counter data inputs to store this instruction. A load control bit must be added to the microword for the instruction register, which must load prior to the counter load (see Figure 2-5). This scheme requires that the op code equal the high-order bits of the start address, with the low-order bits tied to logical 0. This is necessary to allow the starting addresses to be separated by the minimum number of addresses required by the longest microroutine.

Assume that no machine instruction is anticipated to take more than 16 microinstructions to execute. Also, assume a 12-bit address and a 4K PROM memory. The op code must then be no more than 8 bits in length, and the lower 4 bits of the counter data inputs must be tied low. Sixteen steps are allowed per microroutine, and up to 256 different start addresses are possible with this configuration.

The clock pulse required by the controller has not changed. Remember also that the width of the memory is not a function of its depth.

This scheme is adequate if (1) there is sufficient room in the PROM memory, (2) spare locations are acceptable, and (3) no microroutine exceeds 16 steps. If a microroutine exceeds 16 steps, it would overrun a start address, reducing the number of op codes possible; this may still be acceptable. Short routines leave discontinuous unused areas scattered throughout the PROM memory; this may also be acceptable.

# **Mapping PROM**

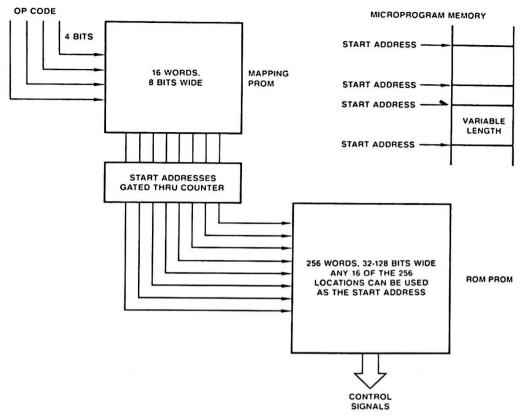

If fragmented space and reduced available op codes are not acceptable, one solution is to add a mapping PROM between the instruction register and the counter. The op code is the address into the map, which in

Figure 2-5. Basic CCU. (x, number of bits in op code; n, number of bits in counter address)

turn outputs the full start address of the microroutine to the counter, as shown in Figure 2-6. Start addresses may now be assigned at any location in the PROM memory rather than being equidistant from one another, and routines may be compacted to delete excessive fragmented space. (It is a good idea to allow some unused areas within the PROM to allow for enhancement changes.) The final placement of the routines in the production PROMs should be done after the debug cycle to minimize mapping PROM changes. This is where a development system is used to advantage.

Another feature may be added once a mapping PROM approach is chosen. The mapping PROM may be made larger than required for normal running and contain address lines driven by switches to allow a

Figure 2-6. Mapping PROM.

Privileged State, where all op codes are valid, and a Normal State, where certain op codes are invalid, "trapping out" to an error trap address in the control memory. The control memory would not necessarily be larger than before.

Also, the mapping PROM and the PROM memory may be set up for future expansion and expansion address lines merely left disconnected or the PROMs left unused in the added areas. (The usual approach is to leave the PROM chips off the board.) It is easier to provide for expansion now than to do a redesign later.

The CCU is shown in Figure 2-7. A fairly reasonable control system has been constructed which is acceptable if all of the microroutines are simple sequences.

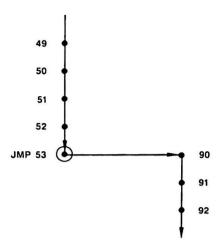

#### **Unconditional Branch**

Often routines may start differently but end with the same steps. Also, once starting addresses are mapped, it might be found that a routine needs to be extended. For these and other cases, the existence of a GO TO or unconditional branch next-address control is desirable. The in-

Figure 2-7. CCU with mapping PROM.

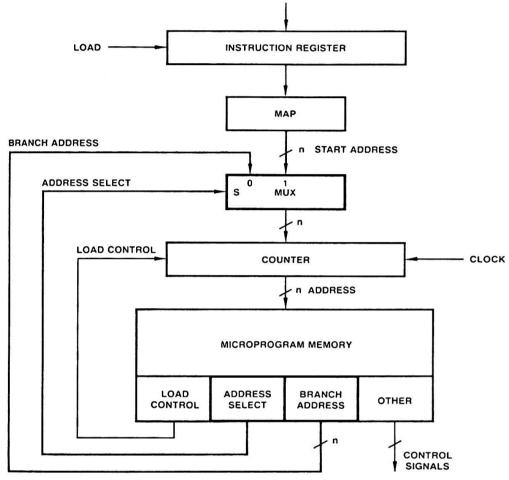

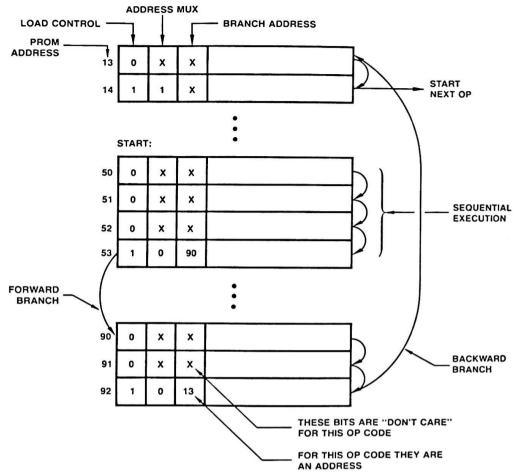

struction flow is shown in Figure 2-8. This instruction causes the counter to be loaded with the desired next address, which is not in sequence with the current address. This is not a start address; therefore the map is not involved. Instead, the microword width must be expanded as shown in Figure 2-9 to contain a branch address field, up to n bits wide, and a next-address-select field. The map and the branch address lines would be input to a 1-of-2 MUX network, n bits wide, with the MUX select operated by the address selection field of the microword. The MUX outputs are the inputs to the counter, as shown in Figure 2-10.

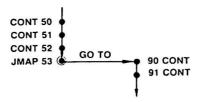

A sample piece of microcode, shown in Figure 2-11, highlights the load control to the counter, the address MUX select, and the branch address field. Assume that the program start address is at address 50. Execution is then seen to be sequential until address 53, which loads the counter (LDCTL = 1) with a branch address (ADR MUX = 0) supplied at address 53 (BR ADR = 90). The next microinstruction executed is at address 90. Address 90 causes a branch back to address 13.

Figure 2-8. Flow diagram of unconditional jump—the GO TO statement. (JMP, jump)

Address 14 causes the counter to be loaded (LDCTL = 1) with a new start address (ADR MUX = 1). This is the last step in the routine that began at address 50.

The width of the branch address field, B, could be less than n, restricting the allowable range of the branch (for example, by leaving the n-B high-order bits unchanged). This complicates the task for the microprogrammer and should be avoided by beginning designers. Good programming practices will require that the various parts of the routines be kept in a relatively compact area, if possible, without artificial enforcement.

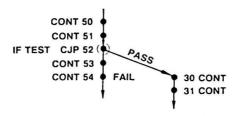

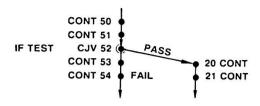

# **Conditional Branch**

It is sometimes desirable to terminate a microroutine in one of several different ways depending on one or more conditions. The conditions tested could be the various status bit outputs of the ALU based on the result of an operation, such as (1) Z = 1 if ACC = 0, (2) S = 1 if

Figure 2-9. Expanded microword. Width of microword increases with increased flexibility and control.

Figure 2-10. CCU with branch capability.

ACC < 0, (3)  $C_{\rm out} = 1$  if  $|{\rm ACC}| > {\rm range}$ , (4) OVR (overflow) = 1 if error, or (5) on the result of a compare operation. Only one condition is testable at a time. Hardware could be used to combine a number of conditions and to supply one test bit if that combination is expected to occur frequently. A program slow diagram for a conditional branch is shown in Figure 2-12.

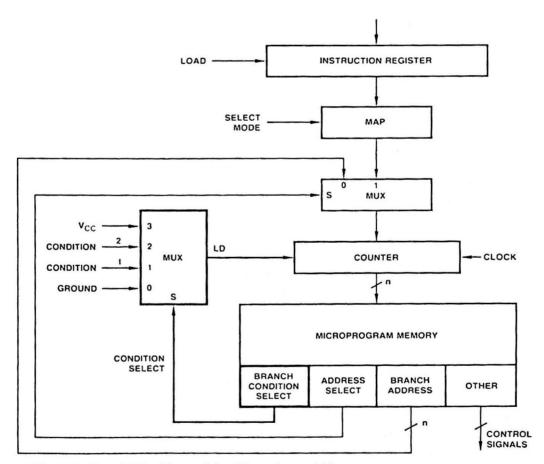

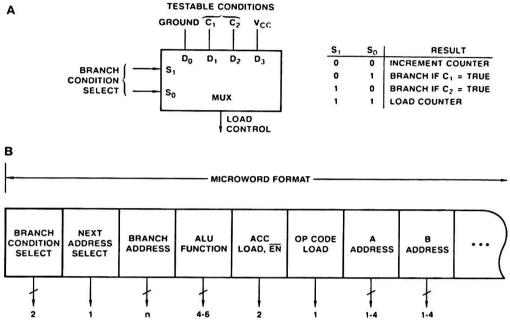

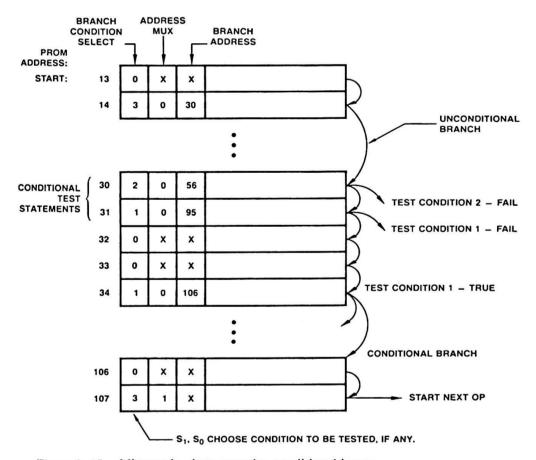

The ability to test a condition and to branch if the condition is true is provided by adding a MUX at the counter load control. The load control field in the microword is changed to a branch condition select, which selects (1) ground (count; no branch), (2) condition 1 or condition 2 (load branch address into counter if true), or (3) Vcc (unconditional branch, load counter). The CCU is shown in Figure 2-13, with its microword format shown in Figure 12-14.

A sample piece of microcode is shown in Figure 2-15 that has both unconditional and conditional branches. As with most programming

Figure 2-11. Microcode, demonstrating the use of jumps. (X bits are "don't care" for this op code; numbered bits are addresses for this op code.)

languages, if a conditional test fails, execution continues sequentially, as shown in statements at addresses 30 and 31. The branch condition select field is 2 bits wide in this example. A wider field would allow a larger MUX and therefore would allow more conditions to be tested.

# **Timing Considerations**

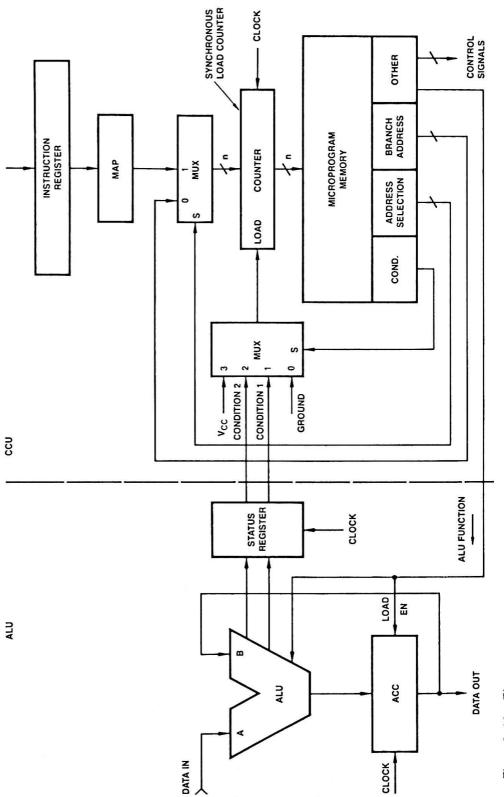

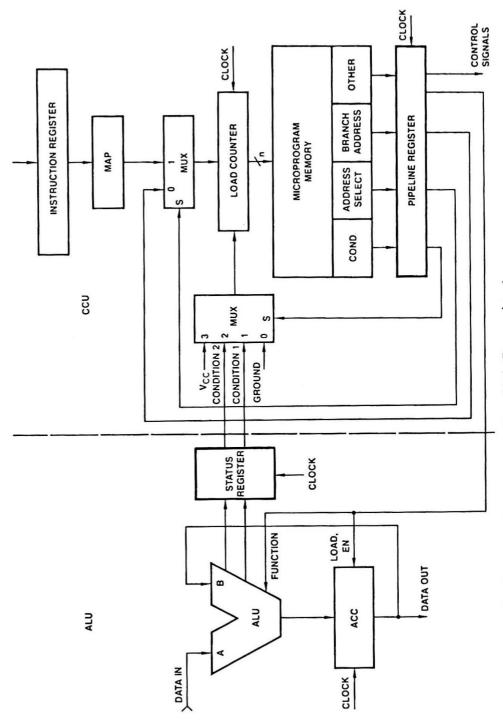

The basic controller evolved so far can be a primitive CCU. Figure 2-16 shows the connections between this CCU and the ALU portions of the simple system described earlier.

The clock pulse width, called the microcycle, is determined from

$$\underline{C}_{p} = \overline{t}$$

counter clock to output  $+ \overline{t}$  PROM read access  $+ \overline{t}$  ALU execution

(For the 2900 family a microcycle is measured from one rising edge

Figure 2-12. Conditional branch flow diagram. "IF-THEN-ELSE" - the conditional branch. (CJP, conditional jump)

Figure 2-13. CCU with conditional branch capability.

Figure 2-14. Microword format for conditional branch. (A) Detail of load control MUX. (B) Detail of microword format.

of the clock to the next. All register write operations occur on the rising edge of the clock.)

# Sequential Timing

A timing diagram is given in Figure 2-17 showing a series of sequential program steps (refer to the CCU-ALU of Figure 2-16). At each rising edge of the clock, the counter increments and settles, and the counter outputs an address to the PROM, whose access time is greater than the counter settling time. As soon as the outputs are stable at the PROM output, execution begins in the ALU. (For now, assume that the operands are available.) On the next rising edge of the clock, the ALU result is gated into the accumulator and the status signals which are being input to the condition MUX are assumed to be stable. (They would normally be gated into a status register on the same clock edge that loads the accumulator.)

# **Branching**

Now assume that a conditional branch is to be executed. On the rising edge of the clock, the status signals from the previous instruction and the result of that instruction are available. Concurrently, the counter has been incremented (Figure 2-18). (Note: this counter is a synchronous loading counter.) The microinstruction i + 1 has been fetched, and this is the conditional branch.

When the outputs are available from the PROM memory, the control

signals are sent to the counter to cause it to load the branch address if the tested condition is true. The MUX select bits, and the condition inputs propagate through the MUX prior to the next rising edge of the clock. No ALU activity occurs.

On the next rising edge of the clock, the branch address enters the counter and the address is input to the PROM. Execution proceeds as before.

There is no difference in the instruction cycle of a branch and a nonbranch instruction in this system. However, while the memory is being accessed, the ALU must remain idle, and while the ALU executes, the memory must remain idle. The minimum total width of the microcycle,  $C_n$ , is the sum of the worst case fetch and execute times.

# **Pipelining**

To improve speed, it is desirable to allow overlap of the ALU and memory fetch processes. This is possible by adding a register at the PROM output, called a pipeline register. The counter is acting as

Figure 2-15. Microcode, demonstrating conditional jumps.

Figure 2-16. Elementary system.

Figure 2-17. Microcycle timing for the system of Figure 2-16 (no branch).

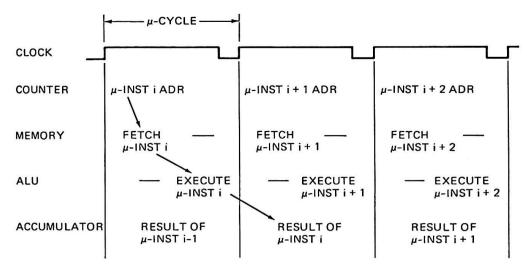

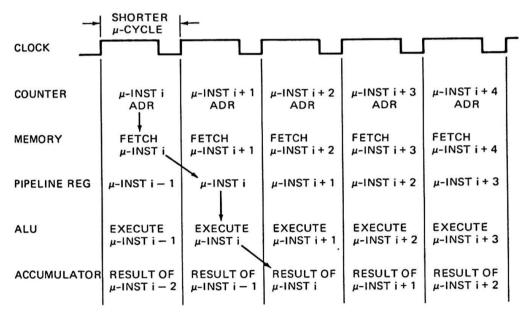

another pipeline register, holding the address that the memory is fetching. The PROM pipeline will hold the current microinstruction under execution. This will allow the counter to move one count ahead and therefore will allow a memory fetch of the i + 1st microinstruction to be overlapped with the execution of the ith microinstruction. The configuration is shown in Figure 2-19.

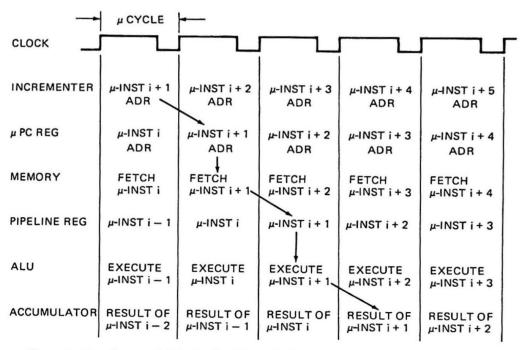

Figure 2-20 shows the timing diagram for sequential execution of this system. When the counter contains the address of microinstruction i, the memory is fetching microinstruction i. The pipeline register con-

Figure 2-18. Microcycle timing for the system of Figure 2-16 (branch). Conditional branch on result of previous microinstruction.

Figure 2-19. Simple system with a pipeline register added. (Reg., register.)

Figure 2-20. Timing for the pipeline system, no branch.

tains microinstruction i-1, which is under execution. If the microinstruction uses the ALU, the ALU is executing the commands of microinstruction i-1 at this time. The accumulator contains the result of the execution of microinstruction i-2; hence the reference to a two-level pipeline.

On the rising edge of the next clock, the counter increments and the memory proceeds to fetch microinstruction i + 1. The pipeline loads with the outputs of the previous memory fetch, microinstruction i, and execution proceeds as before.

The microcycle (no branch) is now

$$\underline{C}_p = \overline{t}$$

counter clock to output  $+ \overline{t}$  PROM read access Or

$$\underline{C}_{p} = \overline{t}$$

pipeline clock to output  $+ \overline{t}$  ALU execution

whichever is greater. If we reasonably assume that the PROM read access time is not longer than the ALU execute time, then the second equation dominates.

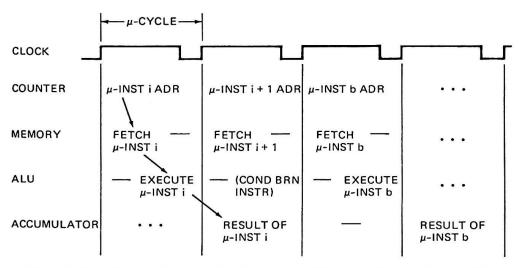

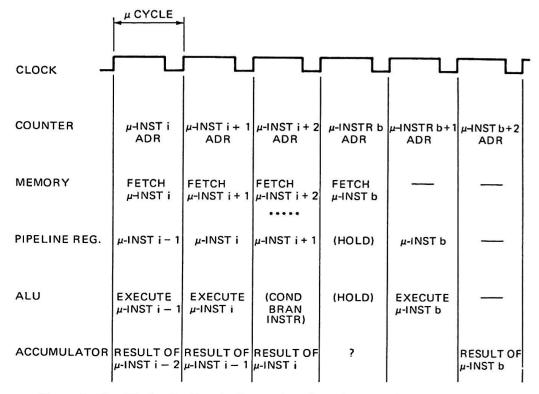

# Pipeline Branch

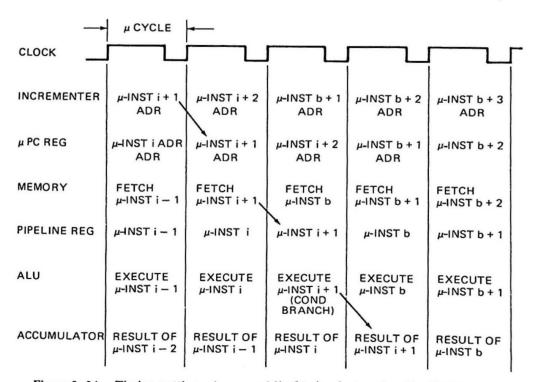

Figure 2-21 examines what happens in this case when a branch is executed. On the rising edge of the first clock, the address of microinstruction i is in the counter and memory is fetching the microinstruction at this address. Execution proceeds as before until the third clock

Figure 2-21. Timing for the pipeline system, branch on result.

signal. At this point the address of microinstruction i + 2 is in the counter and the memory is fetching microinstruction i + 2.

Microinstruction i + 1 is in the pipeline register; this is the conditional branch instruction. The result of microinstruction i is in the accumulator, and the status bits for the ALU produced by the execution of microinstruction i are available. The conditional branch causes the control signals to select the condition to be tested and sets up the load-counter-if-true conditions.

On the next clock edge, microinstruction i + 2 cannot be loaded into the pipeline. A control signal must block one clock pulse to the pipeline register. The branch address is loaded into the counter, and the memory fetches this address. The pipeline still contains microinstruction i + 1, the branch instruction which must not reexecute. Essentially, the execute phase is rendered idle during this microcycle. The next rising edge of the clock loads the branched-to address into the pipeline, and execution proceeds as before.

The problems are obvious. First, a control field and possibly some SSI/MSI controls must be added to prevent cyclic execution of the conditional branch instruction. Second, for one microcycle the ALU is idle and for two microcycles the ACC is unchanged. The process is

referred to as "flushing" the pipeline on execution of a branch instruction; since we have a two-level pipeline, it takes two microcycles to refill the pipe or to recover. This is not desirable if we branch often in a program because the time gained by overlapping memory fetch and ALU execution will be lost. We will ignore the extra hardware and implied programming constraints.

# Improved Architecture

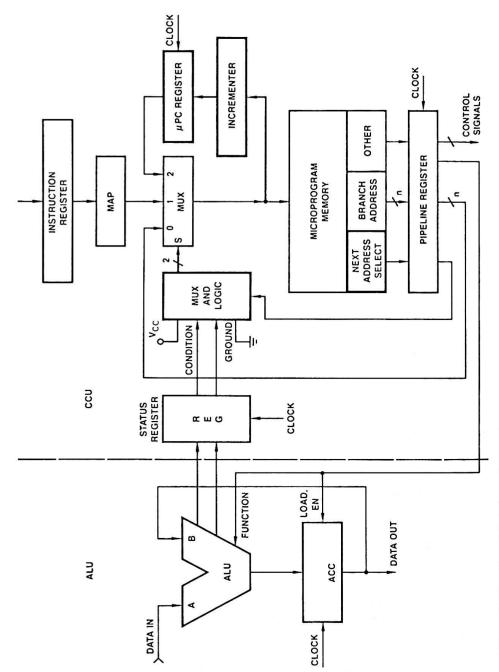

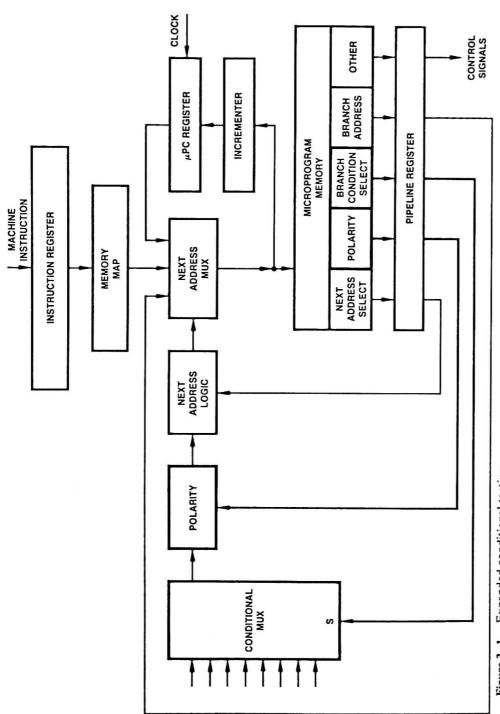

The CCU is improved by placing the next-address MUX to input directly into the PROM to avoid the counter setup time. The counter then becomes one of the three inputs into the next-address MUX. The condition select MUX must be replaced by equivalent logic to generate the two MUX select signals of the new next address MUX.

The counter has moved to a position where it cannot receive a proper input. It must be replaced with a register, called the microprogram counter ( $\mu$ PC) which is connected to the next-address MUX input, formerly assigned to the counter. An incrementer is connected to the PROM memory input and outputs to the  $\mu$ PC. The incrementer always contains the address being fetched plus 1. The outputs of the incrementer are gated into the  $\mu$ PC on the rising edge of the clock. The resulting configuration is shown in Figure 2-22.

#### No Branch

The timing diagram for Figure 2-22 for no-branch execution is shown in Figure 2-23. What exists now is a three-level pipeline. During the first microcycle, the memory is fetching microinstruction i. The address of microinstruction i is in the  $\mu$ PC. The incrementer is one instruction ahead, with the address of microinstruction i+1. The pipeline register contains microinstruction i-1, which is in execution. The accumulator contains the results of microinstruction i-2. The execution proceeds as in earlier diagrams.

# Improved Branching

The difference between the designs is shown in the activity which occurs when a branch is executed, as shown in Figure 2-24.

On the second clock, the memory is fetching microinstruction i+1, and the address of microinstruction i+1 is in the  $\mu$ PC. The address of microinstruction i+2 is in the incrementer. Microinstruction i is in the pipeline register and is being executed by the ALU. The result of microinstruction i-1 is in the accumulator.

On the next clock, microinstruction i+1 is loaded into the pipeline register. This is the conditional branch. The pipeline outputs the controls to the condition select logic which switches the MUX to pass the branch address. At the instant that the clock edge comes up, the  $\mu PC$  is

Figure 2-22. Completed elementary system.

Figure 2-23. Sequential timing for Figure 2-22.

Figure 2-24. Timing to "branch on result" of (microinstruction i ( $\mu$ -INST. i).

loaded with the address of microinstruction i + 2. As soon as the outputs are available, if the MUX has not yet switched, address i + 2 will be sent to memory.

The read access time of the PROM is greater than the propagation delay of the path through the pipeline, condition MUX, and next-address MUX and is greater than the  $\mu$ PC register setup time and the propagation delay of its output through the next-address MUX. Any fluttering of the address inputs occurring from the start of a fetch of microinstruction i+2 and then the switch to the fetch of the branch address is irrelevant, since the memory output is not sensed until the next clock. Therefore during the third cycle the branch address is fetched.

The incrementer now contains the address following the branch address. On the next clock, execution proceeds with no flushing of the pipe, with no extraordinary idle times. This is the desired CCU design.

The cycle time is now

$$\underline{C}_{p} = \overline{I}_{pipeline \ clock} + \overline{I}_{propagate} + \overline{I}_{propagate \ next-address \ MUX} + \overline{I}_{propagate \ next-address \ MUX} + \overline{I}_{propagate \ next-address \ MUX}$$

or

$$\underline{C}_{p} = \overline{I}_{setup \ \mu PC} + \overline{I}_{propagate \ next-address \ MUX} + \overline{I}_{propagate \ next-address \ MUX}$$

or

$$\underline{C}_{p} = \overline{I}_{pipeline \ clock} + \overline{I}_{ALU \ execution} + \overline{I}_{register \ setup \ (ACC: \ status)}$$

whichever is longer (whichever is the critical path).

# Adding Programming Support to the Controller

The CCU developed in Chapter 2 is a high-speed unit capable of n. ing decisions and branching around in the PROM control memory. Any problem may be programmed if GO TO and IF equivalent programming structures exist. The limitations are (1) available programming time, (2) available programming skill, and (3) allowable memory size. The resulting program will run but will be messy at best. As the complexity of the application increases, the need for more powerful programming capabilities increases.

# **Expanded Testing**

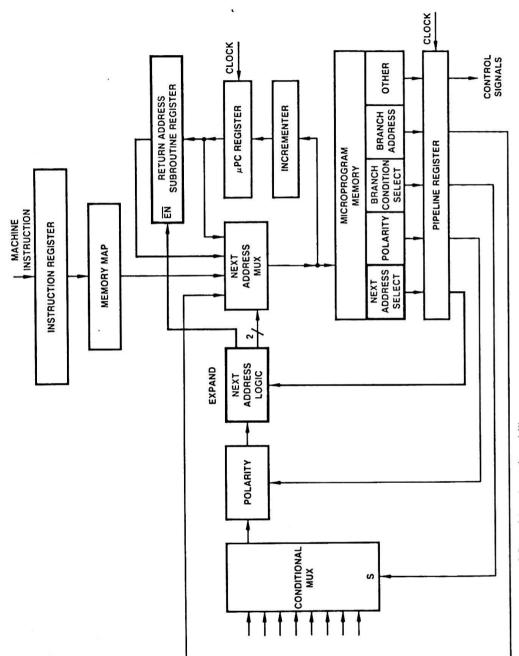

The first change is to expand the number of testable conditions. This is easily done by expanding the branch condition selection MUX which inputs to the next-address MUX selection logic. Next, allow testing to be for IF  $C_i$  or for IF NOT  $C_i$ . This is done by adding a polarity select bit to the microword and a polarity logic block between the condition MUX and the next-address logic block. This improved CCU is shown in Figure 3-1.

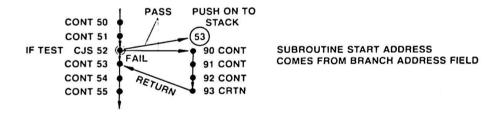

# **Subroutines**

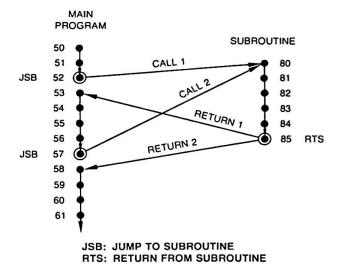

Up to this point, when a branch is executed, the only way to return from the branched-to routine is to execute another branch, and the programmer has to know the exact address. This is fine as long as the

Figure 3-1. Expanded conditional testing.

#### RETURN ADDRESS REGISTER CONTENTS

Figure 3-2. Subroutine flow. (JSB, jump to subroutine; RTS, return from subroutine;  $\lambda$ , garbage.)

branched-to code is accessed by only one source and is required to return to only one source or calling location. When two or more microroutines need to branch to the same piece of code and it is necessary to return from executing that code to the individual calling routine, GO TO and IF structures are inadequate.

It is desirable to provide, instead, a means of storing the address of the calling statement and a means of accessing this storage for the return address. This ability in a higher-level programming language exists as subroutines or procedures.

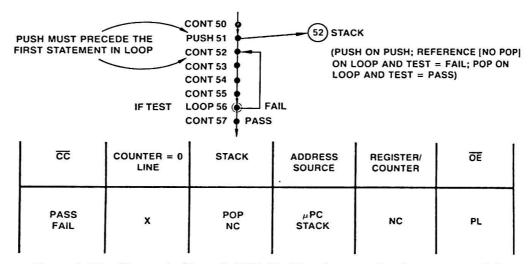

A subroutine can be called from anywhere in a program, and the return to the next statement following the calling statement is made either upon completion of the execution of the subroutine—an unconditional return—or upon the successful test of a condition—a conditional return. Subroutines should be more than one or two statements long to avoid choppy code. (Debug and maintenance features must be stressed in any large microprogram, just as they are in any other programming language.)

A flow of a subroutine calling program is shown in Figure 3-2. When the statement at address 52 calls the subroutine, address 53 is pushed into the return address store. When the return statement at address 85

Figure 3-3. CCU with subroutine ability.

Figure 3-4. Nested subroutine flow.

is executed, the return address is popped from the store which provide, the address of the next microinstruction.

The hardware required to enable the CCU to do this is shown in Figure 3-3. The next-address select logic is expanded to add a load enable to the return address register. When a CALL instruction is executed, a branch to the subroutine is handled as any other branch with the addition that the contents of the  $\mu$ PC are copied into the return address register. The incrementer contains the address of the second step of the subroutine.

To return, the RETURN statement will cause the next-address MUX to select the return address register outputs as the source of the next PROM address, with execution proceeding as if an unconditional branch had occurred.

# **Nested Subroutines**

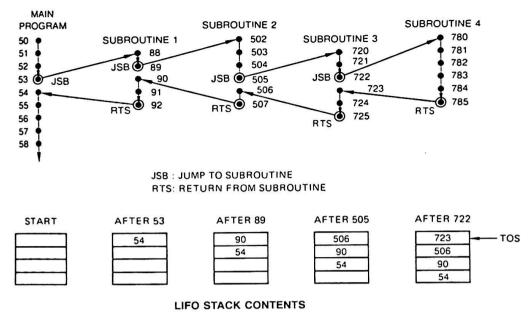

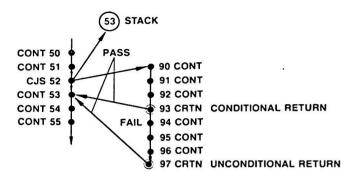

Nested subroutines are flow diagrammed in Figure 3-4. Nested subroutines require more than one return address location and a means of keeping track of the order of the calls. This is accomplished by using a LIFO (last in, first out) stack, pushing and address onto the stack when a CALL is executed and popping an address off, when a RETURN is executed. A stack pointer is used to point to the last entry, which is the top of the stack (TOS).

The same rules that exist for any programming language apply for nested subroutines. When subroutines are nested, the call returns are

Figure 3-5. Adding the FILO stack and TOS pointer.

treated as parentheses in an algebraic equation—that is, if subroutine 3 calls subroutine 4, then subroutine 4 returns to a point in subroutine 3. Subroutine 4 cannot jump out of the subroutine nest in one step. Each return address must be popped from the stack in the order in which it was pushed onto the stack. The TOS pointer can be incremented (for a PUSH) or decremented (for a POP) only by 1.

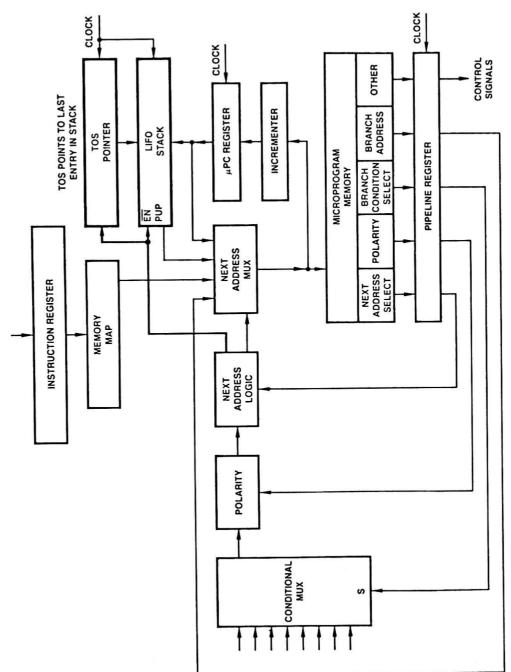

The hardware to allow this is shown in Figure 3-5. A LIFO stack replaces the return address register, and a TOS pointer, a simple counter, has been added. The next-address logic is expanded to provide load enable and PUSH/POP controls to the stack and increment/decrement (INC/DEC) controls to the pointer.

When a subroutine is called, the branch address passes as before. The TOS pointer is incremented, and the  $\mu$ PC is moved into the LIFO stack to the position indexed by the TOS pointer. When a return statement is executed, the contents of the stack location referenced by the TOS pointer are gated by the next-address select MUX into the PROM memory. On the next cycle the TOS pointer is decremented.

#### Stack Size

How large a stack is necessary? Since this stack is to handle microping gram subroutines and since the microprogram is composed of a number of microroutines which also modularize it, deep subroutine nesting is not desirable, nor is it necessary in the general case. For this CCU, a stack four deep is provided and assumed to be adequate. Depending on the ability of the stack to wrap, that is, if the pointer can move from position 4, binary address 11, to position 1, binary address 00 on the fifth successive PUSH without any intervening POP, various types of disasters can occur. The stack may or may not signal that it is full, depending on implementation details. The programmer is cautioned.

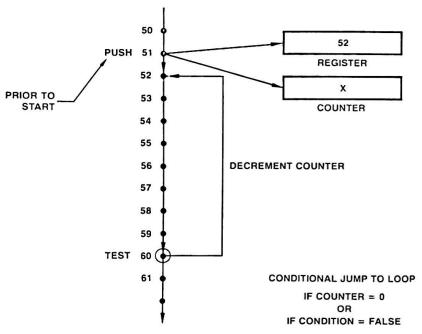

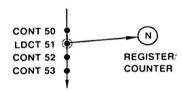

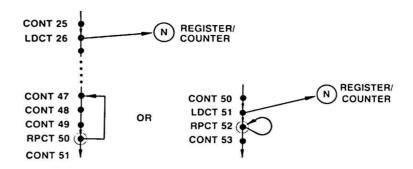

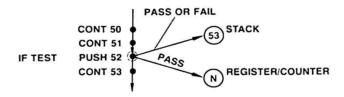

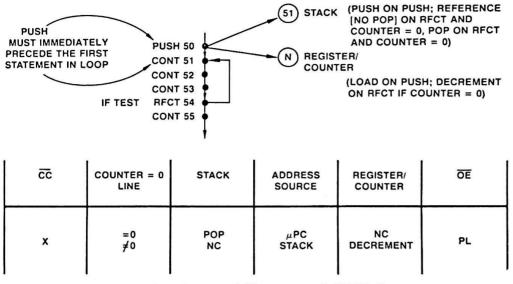

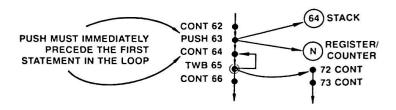

# Loops

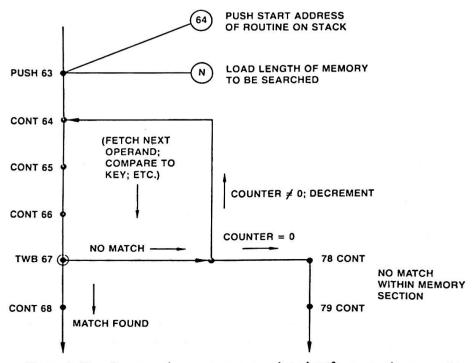

Another desirable programming feature is the ability to repeat one or more statements for some number of times until the number of specified repeats has been completed or until some specified condition occurs. To handle such loops, the starting address must be storable and retrievable and a decrementing or incrementing counter must be provided. The CCU under construction will use a decrementing settable counter. A basic program flow for a loop is shown in Figure 3-6.

#### **Tristate Lines**

The hardware required will require a few changes in the basic CCU. First, there are no more available inputs into the next-address MUX. Rather than expand from a 1-of-4 to a 1-of-8 MUX, which would in-

Figure 3-6. Loop flow. Conditional jump-to loop (CJP) activated if counter  $\neq 0$ , or if CONDITION = FALSE.

crease the microword size, we choose instead to reroute the pipeline branch address lines and have the branch address lines share one of the MUX inputs with the mapping PROM, since a start address and a branch address will never occur at the same time. To allow this sharing, the branch address portion of the pipeline register and the mapping PROM outputs must be tristate lines and must have output enable control signals supplied by the next-address select logic.

#### **Start Address Storage**

The register used to store the start address of the loop is added in parallel with the address bus and may be loaded from the mapping PROM or from the pipeline branch address field. The register is connected to the next-address MUX. Register loading must be controlled by either the next-address logic control or by microinstruction control.

#### Counter

A counter is added such that it is loadable from the mapping PROM or the pipeline branch address field. The technique of allowing a microword format field to be an address in one instruction and a count value in another instruction is called overlapping. The next-address control logic must control the load enable and the decrement control of the counter. The counter provides a status input to the condition MUX, which is used to determine when the contents of the decrementing counter reaches 0. The hardware is shown in Figure 3-7.

Figure 3-7. CCU with loop ability.

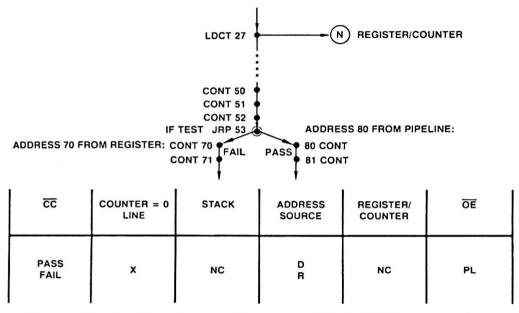

#### Am29811

The next-address control block is now a complex piece of logic. It receives 4 bits of encoded instruction from its field in the microword format  $(I_0 - I_3)$  and also receives 1 bit from the condition MUX output (TEST). It must generate the control signals given in Table 3-1.

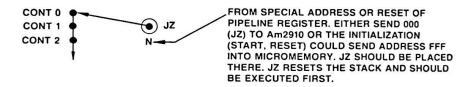

This logic already exists as a single device, the Am29811. The 4 bits of instruction allow 16 different instructions to be generated; their mnemonic list is given in Table 3-2. (Note that TEST is active high, i.e., a test fails if TEST  $\neq$  HIGH.)

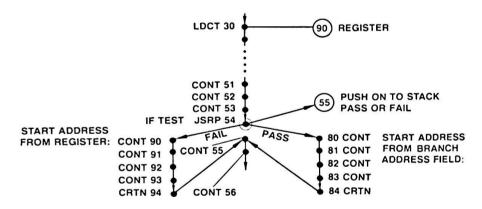

When a loop is to be executed, an LDCT instruction loads the counter with the limit value. This instruction must occur before the loop is executed. Next, the type of loop determines the loop instruction. Three types exist using the Am29811:

- 1. Loop until counter  $\neq 0$ , the starting address is stored in last statement of loop; RPCT.

- Loop until counter = 0, the starting address is stored in the stack prior to the loop beginning; RFCT.

- 3. Loop until a specified test is successful; the starting address has been stored in the stack in advance; LOOP.

Note that the CCU as developed was for the general case and used a register with the loops. The Am29811 uses the register as an alternate subroutine start address  $(R_i)$  or as an alternate branch address in two-way jump instructions. For example, JRP is a jump to register address  $R_i$  or pipeline address  $D_i$  depending on the result of a test. During any microcycle, the register may contain the value of the branch address from any of the previous microinstructions.

# Am2909/11

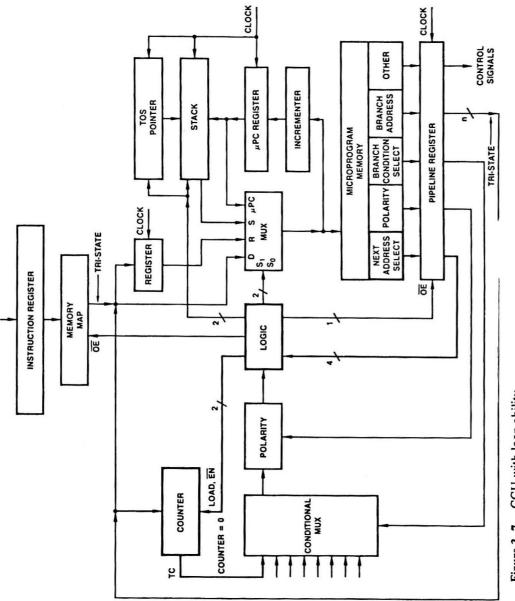

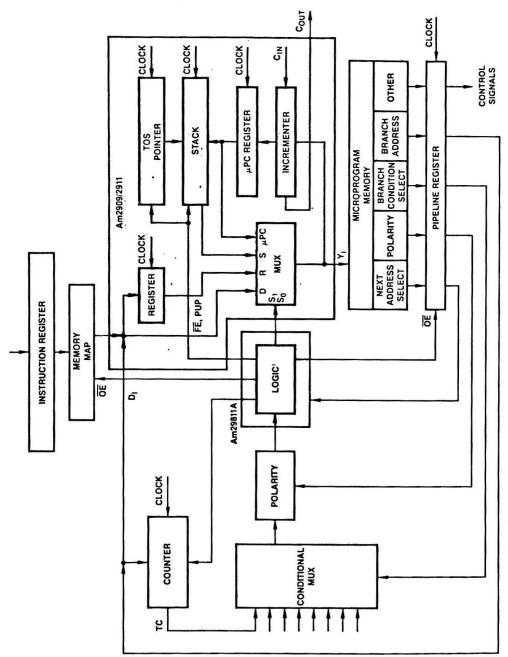

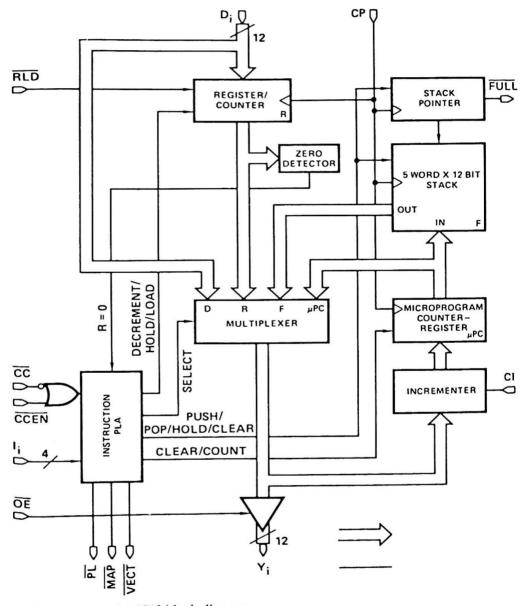

The CCU logic blocks, the register, the stack, the pointer, the  $\mu$ PC, the incrementer, and the next-address select MUX all exist as a single device, the Am2909/11 microprogram sequencer (see Figure 3-8).

| Signal             | Definition                        |  |  |  |

|--------------------|-----------------------------------|--|--|--|

|                    | O Andread In the PROM             |  |  |  |

| MAPE               | Output enable, mapping PROM       |  |  |  |

| PLE                | Output enable, pipeline           |  |  |  |

| S,, S <sub>o</sub> | 2 bits of next-address MUX select |  |  |  |

| FE                 | File (stack) enable               |  |  |  |

| PUP                | Stack PUSH/POP control            |  |  |  |

| CNT LOAD           | Counter load enable               |  |  |  |

| CNT E              | Counter decrement enable          |  |  |  |

Table 3-1 Am29811 Control Signals

Table 3-2 Am29811 Instruction Table

| CJP         | Conditional jump pipeline (jump if)                              |

|-------------|------------------------------------------------------------------|

| CJPP        | Conditional jump pipeline: POP stack                             |

| CJS         | Conditional jump subroutine from pipeline ( and PUSH)            |

| CJV         | Conditional jump vector (interrupt)                              |

| CONT        | Continue (μpc←μpc+1)                                             |

| CRTN        | Conditional return (and POP)                                     |

| JMAP        | Jump to map address (next op)                                    |

| JP          | Jump to pipeline address (branch)                                |

| JRP         | Conditional jump register or pipeline                            |

| <b>JSRP</b> | Conditional jump subroutine from register or pipeline (and PUSH) |

| JZ          | Jump to address zero (initialize)                                |

| LDCT        | Load counter and continue                                        |

| LOOP        | Repeat loop, TEST = FAIL, from stack                             |

| PUSH        | Push stack: conditional load counter and continue                |

| RFCT        | Repeat loop, counter ≠ 0, from stack                             |

| RPCT        | Repeat loop, counter ≠ 0, from pipeline                          |

|             |                                                                  |

The Am2909 and Am2911 differ in package size. The Am2911 has one input to the D (direct) position of the next-address MUX, which is shared with the input to the register (R), while the Am2909 has separate inputs for each. The Am2909 also has OR inputs which allow the outputs of the CCU to be ORed logically with outside data.

Both the Am2909 and Am2911 are bit-slice devices, 4 bits wide and expandable to any width. The typical configuration is three Am2909/11 units and one Am29811. The devices are tied together through the  $C_{\rm in}$  and  $C_{\rm out}$  lines of the incrementer.

Three devices can access 2<sup>12</sup> words or a 4K ROM memory. A reasonably sized CCU might have a PROM memory between 4K and 16K. Controllers have smaller memories, usually less than 4K, depending on the particular application.

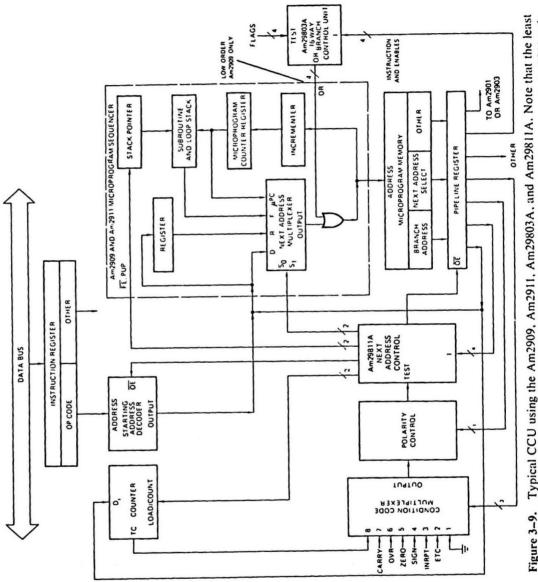

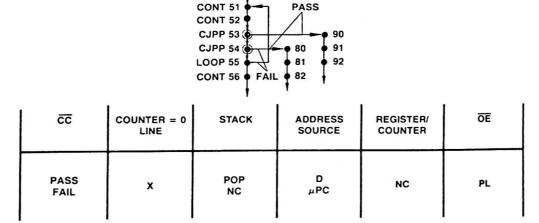

# CASE Statement (Am29803)

There is one other desirable programming structure, the CASE statement or n-way branch. With conditional testing via IF structures, one test is made at a time and branching is to one of two locations. An n-way branch performs one test and branches to one of n locations.

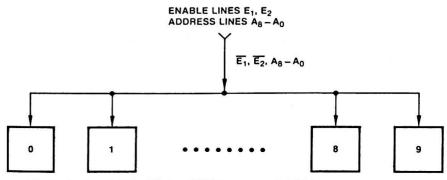

The Am29803 is a testing matrix which connects to the OR inputs of the Am2909. Up to four test inputs may be connected to the Am29803 inputs. A 4-bit encoded instruction selects none, one, two, three, or all four test inputs to produce up to a 16-way branch in one step.

As a sample application consider the situation where two Am2911 units supply the eight high-order address bits and an Am2909 supplies the last four bits. When a test is to be done, the branch address of the

Figure 3-8. CCU with Am2909, Am29811A.

start of the branch table is output by the sequencers. With the configuration indicated, the branch table *must* be located within the microprogram memory so that its first address ends in four zeros (binary). The test produces four bits which are internally ORed to the Am2909 outputs and which select the specific address within the branch table. The branch table is nothing more than a set of jump instructions.

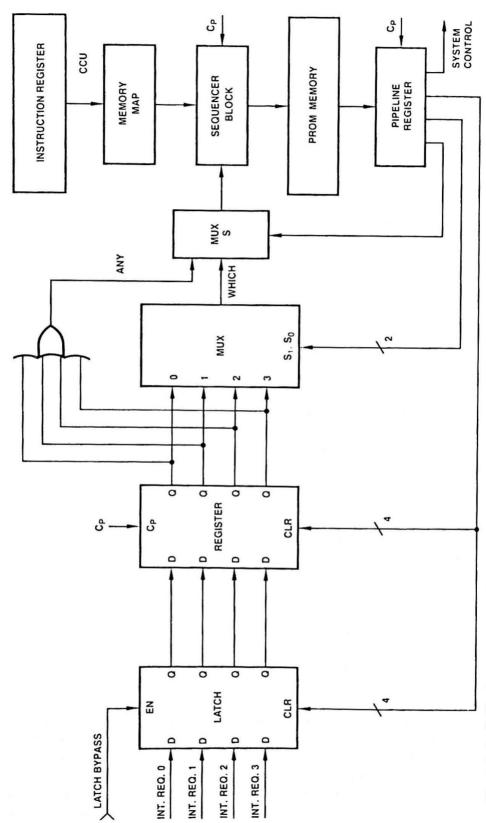

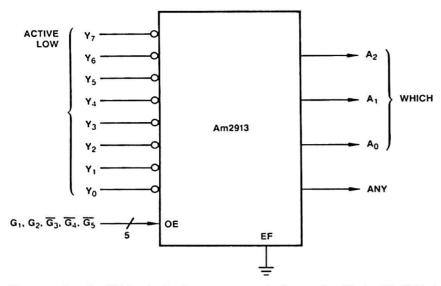

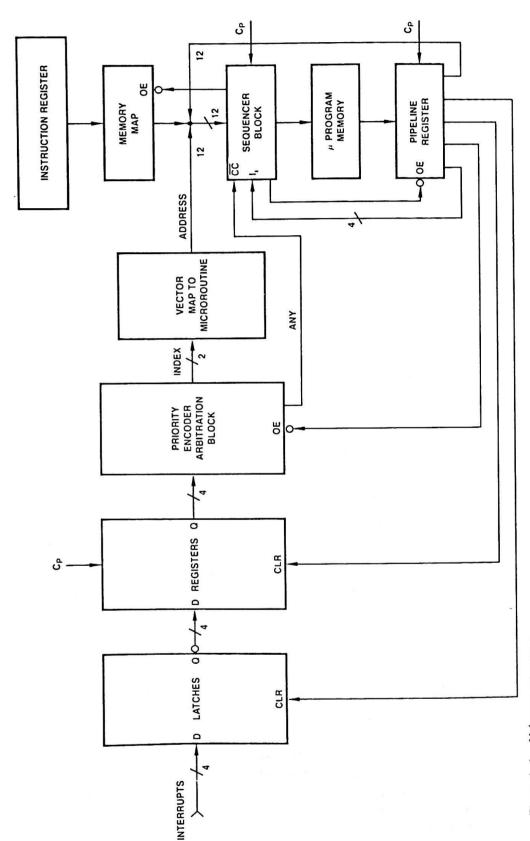

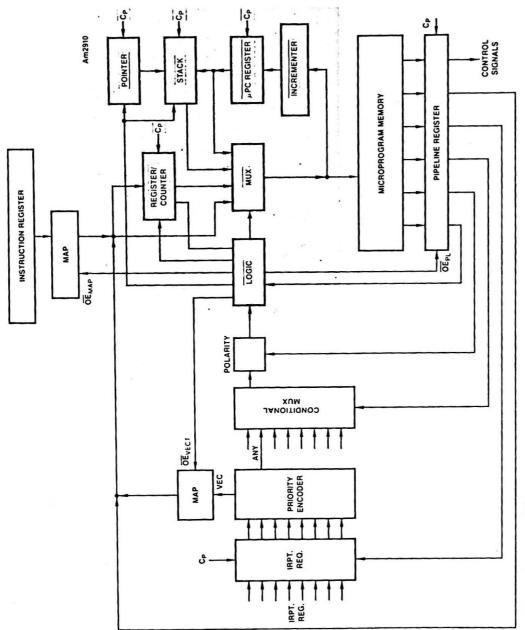

Suppose that you are to test four conditions and decide what to do next, based on the results of the four tests. The software would contain 15 jump instructions for testing, and it would be necessary to execute four instructions to complete the decision. With the Am29803, the four tests are input and an encoded result produced. A 15-deep jump instruction branch table is sufficient, and only two jump instructions need to be executed, one to the branch table and one as a result of landing within the table.